**UNIVERSIDADE DO ESTADO DO ESTADO DE SANTA CATARINA –UDESC

CENTRO DE CIÊNCIAS TECNOLÓGICAS –CCT

DEPARTAMENTO DE ENGENHARIA ELÉTRICA – DEE

PÓS-GRADUAÇÃO EM AUTOMAÇÃO INDUSTRIAL – PGAI**

**Formação: Mestrado em Automação Industrial**

**DISSERTAÇÃO DE MESTRADO OBTIDA POR

Julio Cesar Raycik**

**PROJETO DE UM RETIFICADOR DE CORRENTE REVERSÍVEL

COM ALTO FATOR DE POTÊNCIA E CONTROLE DIGITAL

IMPLEMENTADO EM DSP**

**Apresentado em 18/02/2005 perante a Banca Examinadora:**

**Prof. Dr. Marcello Mezaroba – Orientador – CCT/UDESC**

**Prof. Dr. Samir Ahmad Mussa – UNIJUI**

**Prof. Dr. Antônio Heronaldo de Sousa – Orientador – CCT/UDESC**

**Prof. Dr. Alcindo do Prado Jr. – CCT/UDESC**

**UNIVERSIDADE DO ESTADO DO ESTADO DE SANTA CATARINA –UDESC

CENTRO DE CIÊNCIAS TECNOLÓGICAS –CCT

DEPARTAMENTO DE ENGENHARIA ELÉTRICA – DEE

PÓS-GRADUAÇÃO EM AUTOMAÇÃO INDUSTRIAL – PGAI**

**DISSERTAÇÃO DE MESTRADO**

**Mestrando: Julio Cesar Raycik, Eng.**

**Orientador: Marcello Mezaroba, Dr. Eng.**

**PROJETO DE UM RETIFICADOR DE CORRENTE REVERSÍVEL

COM ALTO FATOR DE POTÊNCIA E CONTROLE DIGITAL

IMPLEMENTADO EM DSP**

Dissertação submetida à Universidade

do Estado de Santa Catarina como parte

dos requisitos para a obtenção do grau

de Mestre em Automação Industrial.

Joinville

2005

## FICHA CATALOGRÁFICA

|                                                                                                                                    |                                       |

|------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|

| <b>NOME:</b> RAYCIK, Julio Cesar                                                                                                   |                                       |

| <b>DATA DA DEFESA:</b> 18/02/2005                                                                                                  |                                       |

| <b>LOCAL:</b> Joinville, CCT/UDESC                                                                                                 |                                       |

| <b>NÍVEL:</b> Mestrado                                                                                                             | <b>Número de Ordem:</b> 18 -CCT/UDESC |

| <b>FORMAÇÃO:</b> Automação Industrial                                                                                              |                                       |

| <b>ÁREA DE CONCENTRAÇÃO:</b> Controle e Eletrônica de Potência                                                                     |                                       |

| <b>TÍTULO:</b> Projeto de um Retificador de Corrente Reversível com Alto Fator de Potência e Controle Digital Implementado em DSP. |                                       |

| <b>PALAVRAS-CHAVES:</b> Controlador DSP, Conversor, Ponte Completa, Retificador, Controle Digital, Eletrônica de Potência.         |                                       |

| <b>NÚMERO DE PÁGINAS:</b> xxiii,134 p.                                                                                             |                                       |

| <b>CENTRO/UNIVERSIDADE:</b> Centro de Ciências Tecnológicas da UDESC.                                                              |                                       |

| <b>PROGRAMA:</b> Pós-Graduação em Automação Industrial – PGAI                                                                      |                                       |

| <b>CADASTRO CAPES:</b>                                                                                                             |                                       |

| <b>ORIENTADOR:</b> Dr. Marcello Mezaroba                                                                                           |                                       |

| <b>PRESIDENTE DA BANCA:</b> Dr. Marcello Mezaroba                                                                                  |                                       |

| <b>MEMBROS DA BANCA:</b>                                                                                                           |                                       |

| Dr. Samir Ahmad Mussa                                                                                                              |                                       |

| Dr. Antônio Heronaldo de Sousa                                                                                                     |                                       |

| Dr. Alcindo do Prado Jr.                                                                                                           |                                       |

## DEDICATÓRIA

*À minha amada Catarina

e aos meus pais, Narcizo e

Mercedes.*

## AGRADECIMENTOS

A Deus, pelas oportunidades e bênçãos derramadas em minha vida.

Ao Professor Marcello Mezaroba pela orientação e admirável sabedoria, pela enorme motivação, pela ajuda incomparável, pela amizade e pelo privilegio de seus ensinamentos neste um ano e meio de trabalho.

A Banca Examinadora pelas contribuições e correções.

Ao Professor Alessandro Batschauer também pela ajuda e ensinamentos valiosos e pela transmissão de seus conhecimentos na área da Eletrônica de Potência.

Ao grande amigo, Mestrando Valmor Adami Jr. pelos grandes conhecimentos de programação e pela ajuda incansável e por estar sempre ao meu lado.

Aos membros da banca examinadora pelas revisões, correções e sugestões.

Ao colega Eng. Fabiano Cardoso pela ajuda e companheirismo.

Ao Engenheiro Roberto Andrisch pelos esclarecimentos e auxílios.

Aos brilhantes Professores do Programa de Mestrado da Universidade do Estado de Santa Catarina-Joinville, em especial aos Professores Alcindo Prado Junior e Antônio Heronaldo de Sousa, pela infinidável carga de conhecimento.

Aos demais estimáveis colegas do mestrado e graduação que me ajudaram nesta caminhada.

Ao Seu Ernesto Warnecke e Dona Denise Aidar Warnecke pela ajuda e apoio.

A Catarina pela paciência, apoio e amor.

A Ciência pela inspiração, orientação e esclarecimento.

Resumo da Dissertação apresentado à UDESC como parte dos requisitos necessários para obtenção do grau de Mestre em Automação Industrial.

**PROJETO DE UM RETIFICADOR DE CORRENTE REVERSÍVEL COM ALTO FATOR DE POTÊNCIA E CONTROLE DIGITAL IMPLEMENTADO EM DSP**

**Julio Cesar Raycik**

Fevereiro de 2005

Orientador: Marcello Mezaroba, Dr.

Área de Concentração: Eletrônica de Potência.

Palavras-chaves: Controlador DSP, Conversor, Ponte Completa, Retificador, Controle Digital, Eletrônica de Potência.

Número de Páginas: xxiii, 134

**RESUMO**

O principal objetivo deste trabalho é o projeto e a montagem de um retificador de corrente reversível com alto fator de potência, através do controle de corrente utilizando o método dos valores instantâneos. O controle será feito através de um Processador Digital de Sinais (DSP). Apesar de vários estudos já terem sido realizados nesta área, este campo é recente entre os pesquisadores da UDESC, por isso a contribuição deste trabalho está no domínio da tecnologia do controle digital para emprego em trabalhos futuros. É realizado neste o estudo qualitativo e quantitativo do conversor, onde é apresentada a estrutura do conversor, o princípio de funcionamento nos diversos quadrantes de operação e a definição das principais equações que regem a dinâmica do conversor. O trabalho também apresenta o projeto do circuito de potência e do compensador digital. Por fim traz os resultados obtidos através de simulações, o estudo do processador digital de sinais e a estrutura montada para os testes práticos das leis de controles, além dos resultados práticos obtidos.

Abstract of Dissertation presented to UDESC as a partial fulfillment of requirements for the degree of Master in Industrial Automation.

**DESIGN OF ONE CURRENTE REVESIBLE RETIFIER WITH HIGH POWER

FACTOR AND DIGITAL CONTROL IMPLEMENTED IN DSP**

**Julio Cesar Raycik**

2005, February

Advisor: Marcello Mezaroba, Dr.

Área of Concentration: Power Eletronics.

Palavras-chaves: DSP Controler, Current Retifier, Full Brigdh, Retifier, Digital Control, Power Electronic.

Number of Pages: xxiii, 134

**ABSTRACT**

The target of this work is the design and assembly of a reversible current rectifier with high power factor, by current control using the instantaneous values. The control is made by one Digital Signal Processor (DSP). Though many studies already have been made in this area, this field is recently between the UDESC's research, So, this work's contributions is in the technology upper hand of digital control to use in futures research. A qualitative and quantities study is made, where is showed the converter structure, the working principles in the almost working site and the main equation definition that are used in this converter. This work show too the power circuits and digital control design. And in the end show the results get by simulation, the digital processor study and results get though the assembled structure for practical tests of control lows implement in laboratory.

## ÍNDICE

|                                  |            |

|----------------------------------|------------|

| <b>FICHA CATALOGRÁFICA .....</b> | <b>III</b> |

| <b>DEDICATÓRIA .....</b>         | <b>IV</b>  |

| <b>AGRADECIMENTOS.....</b>       | <b>V</b>   |

| <b>RESUMO .....</b>              | <b>VI</b>  |

| <b>ABSTRACT .....</b>            | <b>VII</b> |

### CAPITULO 1

|                                                   |          |

|---------------------------------------------------|----------|

| <b>1 ESTUDO QUALITATIVO DO CONVERSOR.....</b>     | <b>1</b> |

| 1.1 A Estrutura do Conversor.....                 | 1        |

| 1.2 Princípios de Funcionamento.....              | 2        |

| 1.3 Etapas de Funcionamento como Retificador..... | 5        |

| 1.3.1 Funcionamento no 1º Quadrante .....         | 5        |

| 1.3.2 Funcionamento no 3º Quadrante .....         | 8        |

| 1.4 Conclusões.....                               | 12       |

### CAPITULO 2

|                                                        |           |

|--------------------------------------------------------|-----------|

| <b>2 ANALISE QUANTITATIVA DO CONVERSOR.....</b>        | <b>13</b> |

| 2.1 Análise Quantitativa .....                         | 13        |

| 2.2 Definição das Principais Equações .....            | 15        |

| 2.3 Esforços nos Componentes.....                      | 18        |

| 2.3.1 Equações para Esforços das Chaves .....          | 18        |

| 2.3.2 Equações para Esforços do Diodo.....             | 20        |

| 2.3.3 Equações para Cálculo do Capacitor .....         | 22        |

| 2.3.4 Equações para o Calculo do Indutor .....         | 25        |

| 2.4 Definição das Equações para o Cálculo Térmico..... | 28        |

|                   |                                                                                                   |           |

|-------------------|---------------------------------------------------------------------------------------------------|-----------|

| 2.5               | <b>Cálculo Térmico .....</b>                                                                      | <b>31</b> |

| 2.6               | <b>Conclusões.....</b>                                                                            | <b>32</b> |

| <b>CAPITULO 3</b> |                                                                                                   |           |

| <b>3</b>          | <b>PROJETO DO CIRCUITO DE POTÊNCIA.....</b>                                                       | <b>33</b> |

| 3.1               | <b>Definição dos Parâmetros para o Projeto.....</b>                                               | <b>33</b> |

| 3.1.1             | <b>Cálculos das Correntes.....</b>                                                                | <b>34</b> |

| 3.1.2             | <b>Cálculo do Indutor .....</b>                                                                   | <b>34</b> |

| 3.1.2.1           | Cálculo da indutância: .....                                                                      | 34        |

| 3.1.2.2           | Cálculo do indutor: .....                                                                         | 34        |

| 3.1.3             | <b>Cálculo do Capacitor de Saída .....</b>                                                        | <b>36</b> |

| 3.1.4             | <b>Esforços nos Transistores .....</b>                                                            | <b>36</b> |

| 3.1.5             | <b>Esforços dos Diodos .....</b>                                                                  | <b>37</b> |

| 3.2               | <b>Cálculo Térmico .....</b>                                                                      | <b>39</b> |

| 3.2.1             | <b>Perdas por Condução no Transistor.....</b>                                                     | <b>39</b> |

| 3.2.2             | <b>Perdas na Entrada no Transistor .....</b>                                                      | <b>39</b> |

| 3.2.3             | <b>Perdas no Bloqueio o Transistor .....</b>                                                      | <b>39</b> |

| 3.2.4             | <b>Perda Total para o Transistor.....</b>                                                         | <b>40</b> |

| 3.2.5             | <b>Perdas por Condução no Diodo.....</b>                                                          | <b>40</b> |

| 3.2.6             | <b>Perdas por Entrada em comutação no Diodo .....</b>                                             | <b>40</b> |

| 3.2.7             | <b>Perdas Totais no Diodo .....</b>                                                               | <b>40</b> |

| 3.2.8             | <b>Perdas no Transistor e Didos.....</b>                                                          | <b>41</b> |

| 3.3               | <b>Cálculo Térmico .....</b>                                                                      | <b>41</b> |

| 3.3.1             | <b>Cálculo da temperatura de cápsula para o TRANSISTOR .....</b>                                  | <b>41</b> |

| 3.3.2             | <b>Cálculo da temperatura de cápsula para o DIODO .....</b>                                       | <b>41</b> |

| 3.3.3             | <b>Cálculo da Temperatura do Dissipador. ....</b>                                                 | <b>42</b> |

| 3.3.4             | <b>Especificação da Resistência Dissipadora Ambiente Máxima (<math>R_{da(th)}</math>).<br/>42</b> |           |

| 3.3.5             | <b>Escolha do Dissipador .....</b>                                                                | <b>42</b> |

| 3.4               | <b>Conclusões.....</b>                                                                            | <b>42</b> |

## CAPITULO 4

|                                                                         |           |

|-------------------------------------------------------------------------|-----------|

| <b>4 PROJETO DO SISTEMA DE COMANDO E CONTROLE .....</b>                 | <b>44</b> |

| <b>4.1 Introdução.....</b>                                              | <b>44</b> |

| <b>4.2 Visão Geral do Diagrama de Controle.....</b>                     | <b>44</b> |

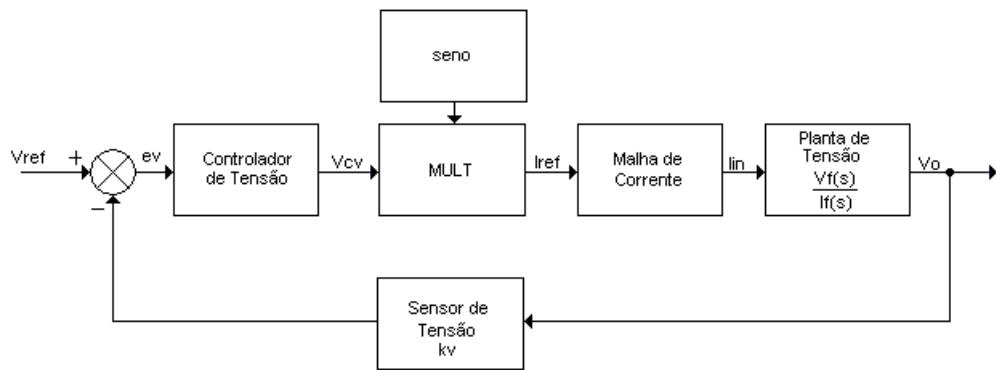

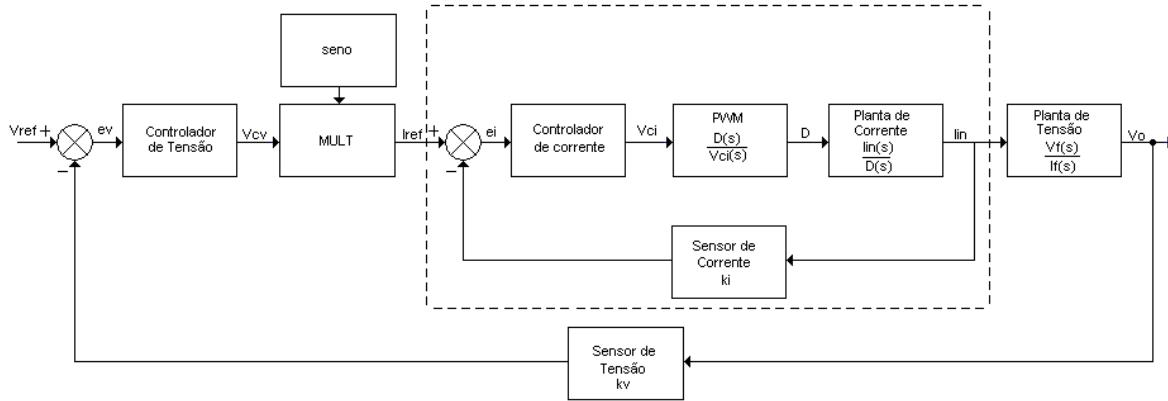

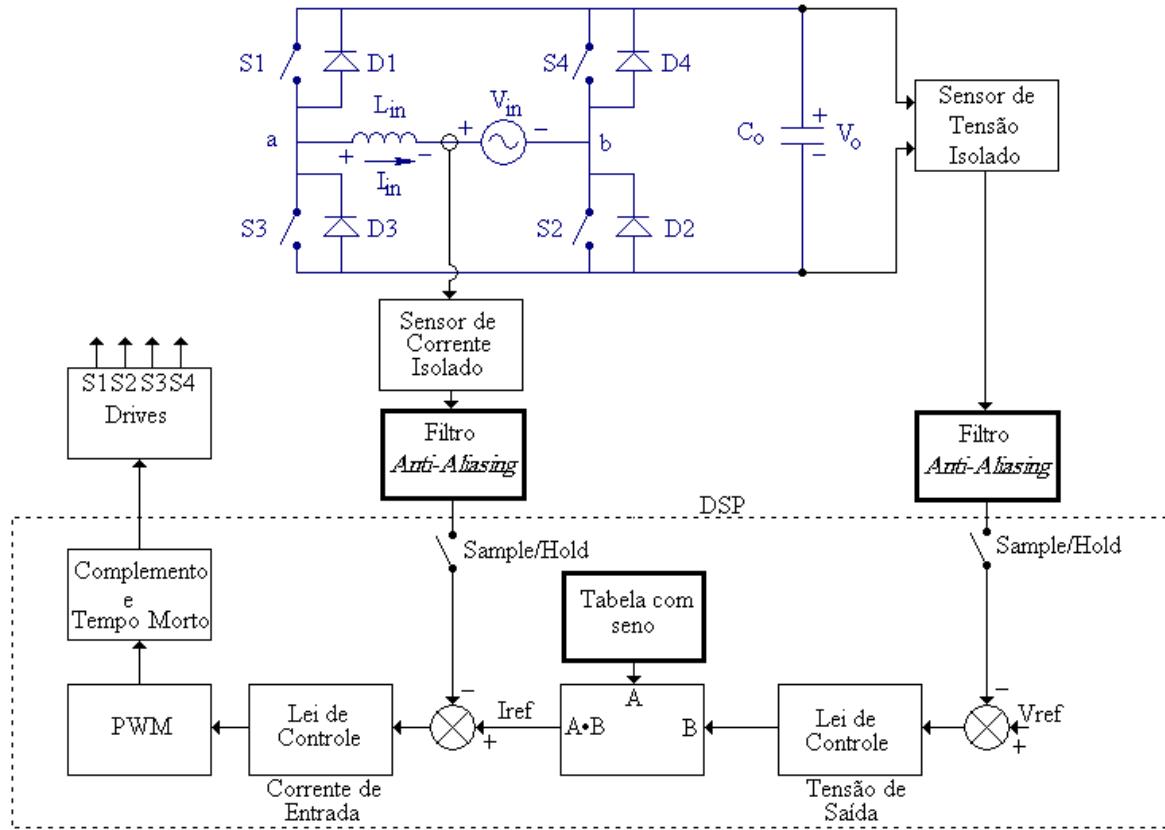

| <b>4.2.1 Malha de corrente.....</b>                                     | <b>44</b> |

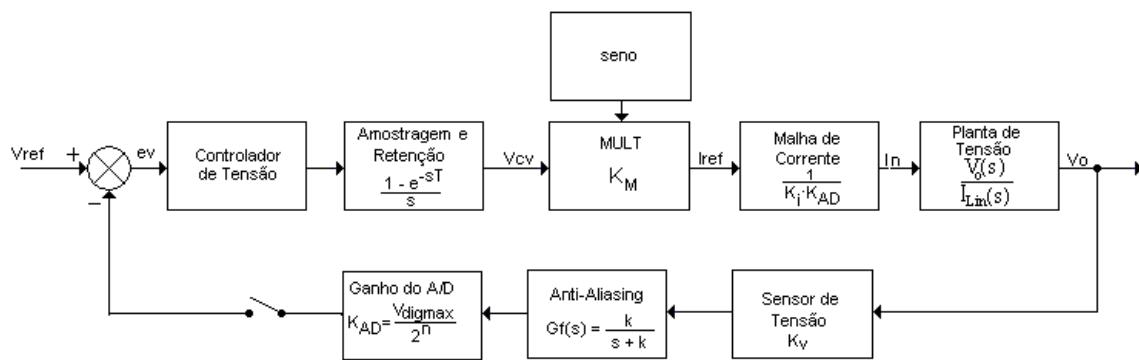

| <b>4.2.2 Malha de Tensão.....</b>                                       | <b>46</b> |

| <b>4.3 Diagrama de Blocos de Controle Usando DSP.....</b>               | <b>48</b> |

| <b>4.4 Funções de Transferência do Retificador .....</b>                | <b>49</b> |

| <b>4.4.1 Função de Transferência para Controle de Corrente.....</b>     | <b>50</b> |

| <b>4.4.2 Função de Transferência para Controle de Tensão .....</b>      | <b>52</b> |

| <b>4.5 Função de Transferência do filtro anti-aliasing.....</b>         | <b>53</b> |

| <b>4.6 Função de Transferência do Modulador PWM.....</b>                | <b>55</b> |

| <b>4.7 Função de Transferência do Conversor A/D.....</b>                | <b>57</b> |

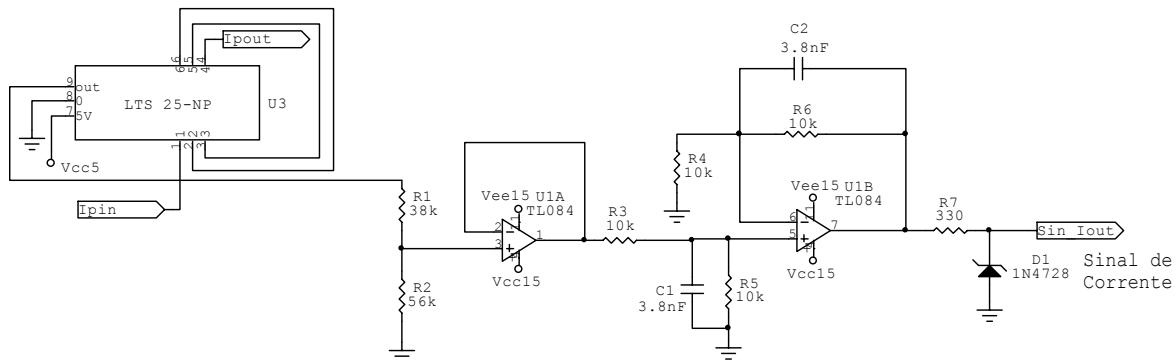

| <b>4.8 Função de Transferência do Sensor de Corrente .....</b>          | <b>57</b> |

| <b>4.9 Metodologia de projeto para controladores digitais.....</b>      | <b>59</b> |

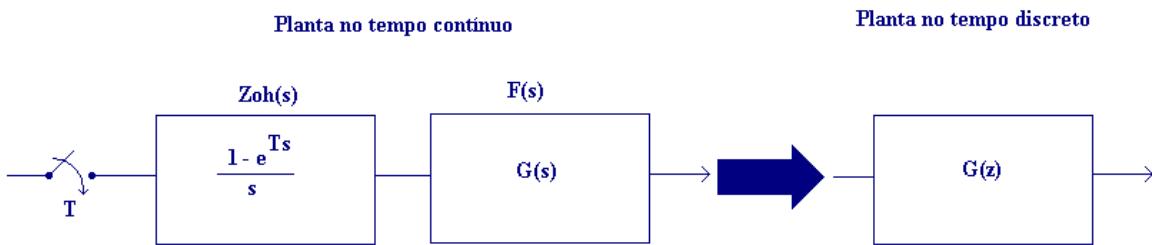

| <b>4.9.1 Transformações Bilineares .....</b>                            | <b>59</b> |

| <b>4.9.2 Transformada z e w.....</b>                                    | <b>60</b> |

| <b>4.9.3 Distorções resultantes da digitalização .....</b>              | <b>62</b> |

| <b>4.10 Procedimento de Projeto dos Compensadores Digitais .....</b>    | <b>64</b> |

| <b>4.11 Projeto do Compensador de Corrente.....</b>                     | <b>65</b> |

| <b>4.11.1 Função de Transferência no Plano s .....</b>                  | <b>65</b> |

| <b>4.11.2 Função de Transferência no Plano z.....</b>                   | <b>66</b> |

| <b>4.11.3 Função de Transferência no Plano w.....</b>                   | <b>67</b> |

| <b>4.11.4 Função de Transferência de Malha Aberta (FTMAi).....</b>      | <b>68</b> |

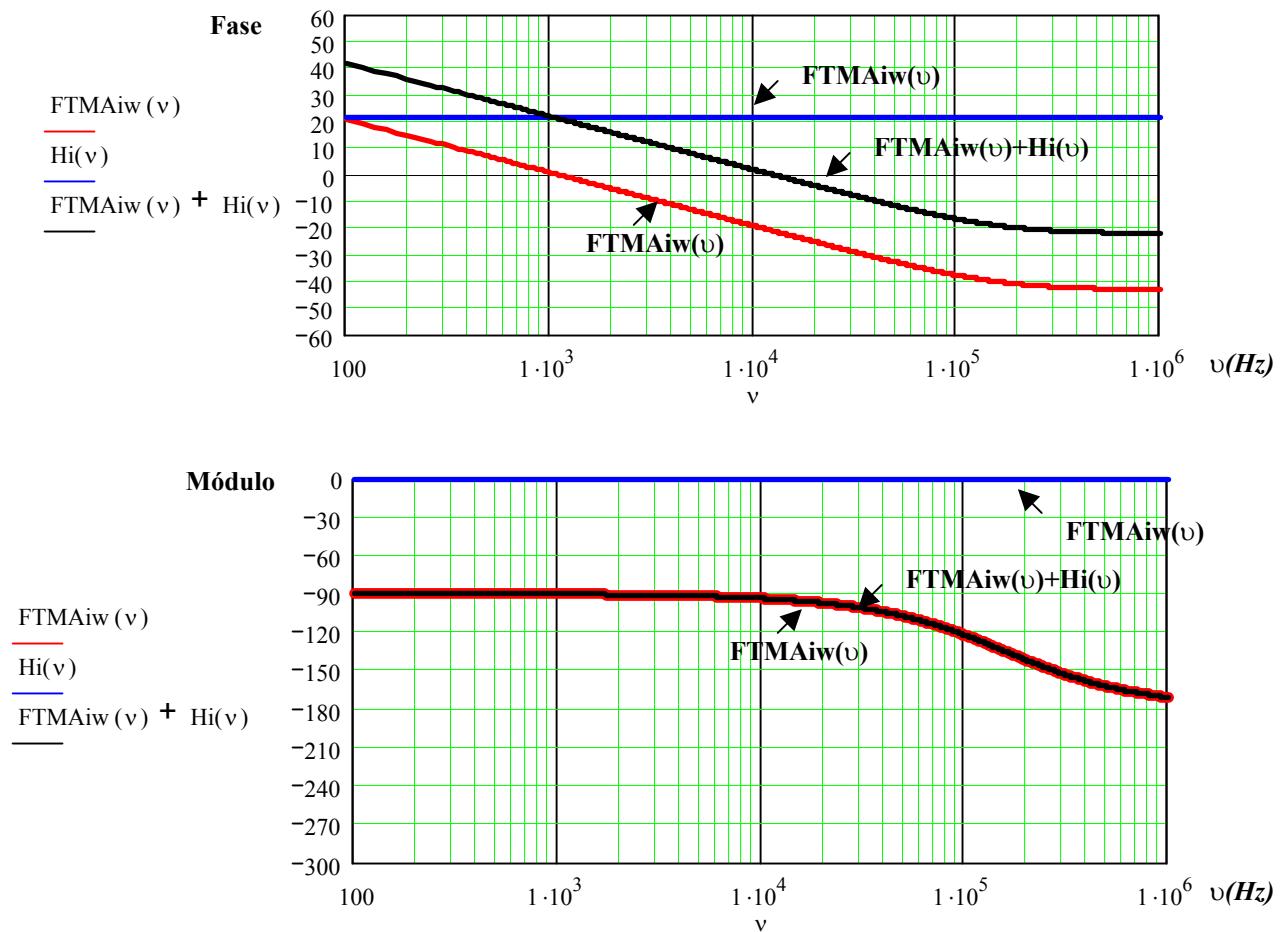

| <b>4.11.5 Análise da resposta em freqüência da FTMAi.....</b>           | <b>69</b> |

| <b>4.11.6 Projeto do Compensador de Corrente.....</b>                   | <b>72</b> |

| <b>4.11.7 Analise da Influência do Compensador.....</b>                 | <b>73</b> |

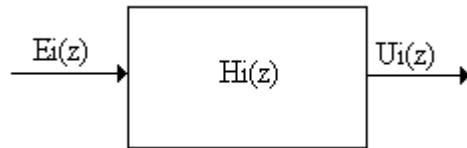

| <b>4.11.8 Transformada Inversa do Compensador .....</b>                 | <b>74</b> |

| <b>4.11.9 Equações de Diferenças para Compensador de Corrente .....</b> | <b>74</b> |

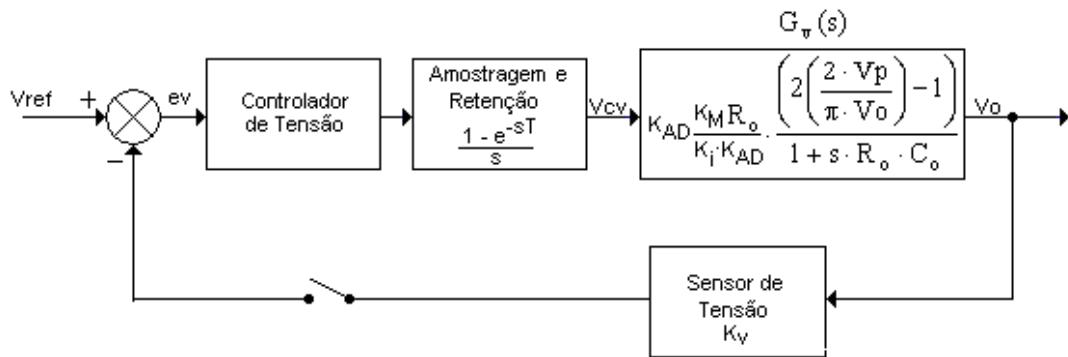

| <b>4.12 Projeto do Controlador de Tensão.....</b>                       | <b>75</b> |

|         |                                                               |    |

|---------|---------------------------------------------------------------|----|

| 4.12.1  | Função de Transferência no Plano s .....                      | 75 |

| 4.12.2  | Função de Transferência no Plano z.....                       | 76 |

| 4.12.3  | Função de Transferência no Plano w.....                       | 77 |

| 4.12.4  | Função de Transferência no Plano de Malha Aberta (FTMAv)..... | 78 |

| 4.12.5  | Ganho do Sensor de Corrente .....                             | 79 |

| 4.12.6  | Análise da resposta em freqüência da FTMAv.....               | 79 |

| 4.12.7  | Projeto do Compensador de Tensão .....                        | 82 |

| 4.12.8  | Analise da Influência do Compensador.....                     | 83 |

| 4.12.9  | Transformada Inversa do Compensador .....                     | 84 |

| 4.12.10 | Equações de Diferenças para Compensador de Corrente .....     | 85 |

| 4.13    | Conclusões .....                                              | 85 |

## CAPITULO 5

|     |                                      |    |

|-----|--------------------------------------|----|

| 5   | SIMULAÇÃO NÚMERICA .....             | 86 |

| 5.1 | Introdução.....                      | 86 |

| 5.2 | Ferramenta para Simulação .....      | 86 |

| 5.3 | Funcionamento como Retificador ..... | 89 |

| 5.4 | Regeneração.....                     | 91 |

| 5.5 | Conclusões.....                      | 94 |

## CAPITULO 6

|       |                                                        |     |

|-------|--------------------------------------------------------|-----|

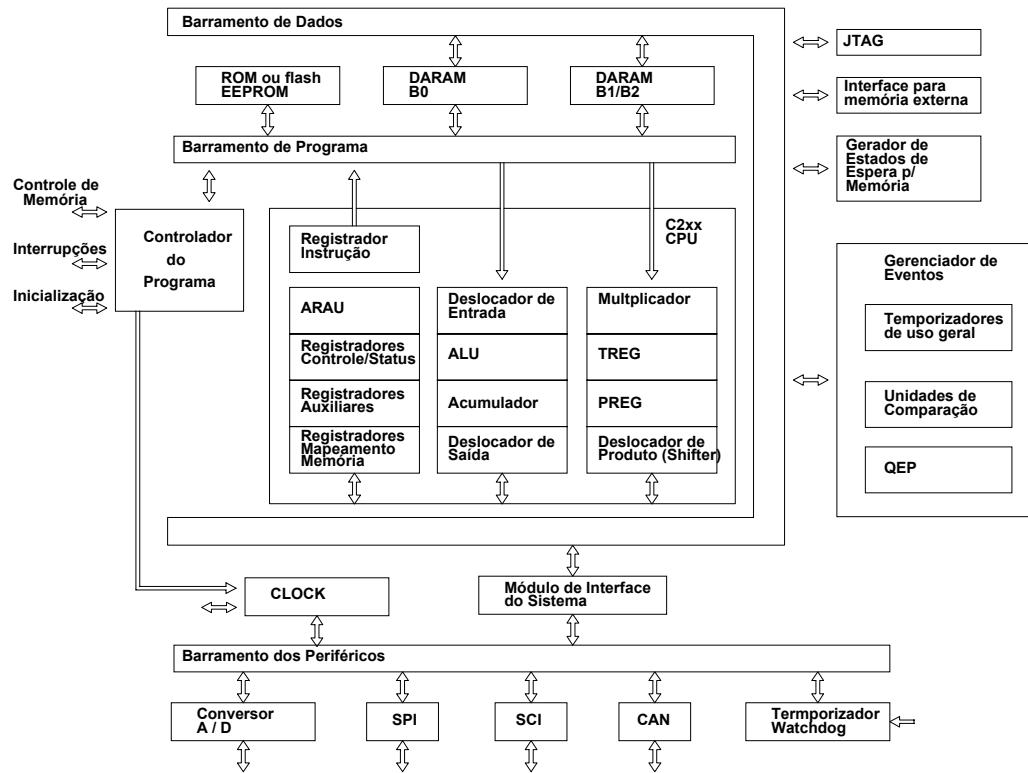

| 6     | PROCESSADOR DIGITAL DE SINAIS - DSP .....              | 95  |

| 6.1   | Introdução.....                                        | 95  |

| 6.2   | A Arquitetura do Processador.....                      | 95  |

| 6.3   | TMS320LF24xx.....                                      | 97  |

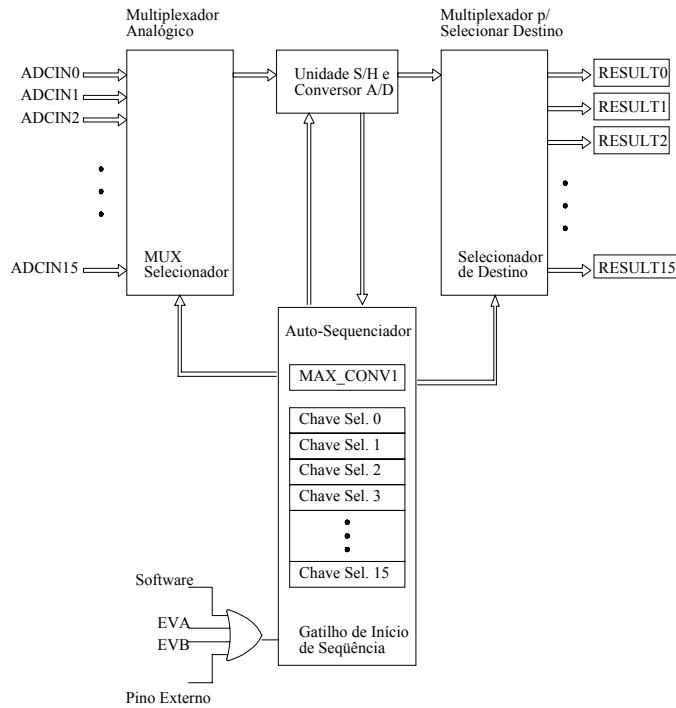

| 6.4   | Conversor Analógico para Digital de 10 Bits (ADC)..... | 101 |

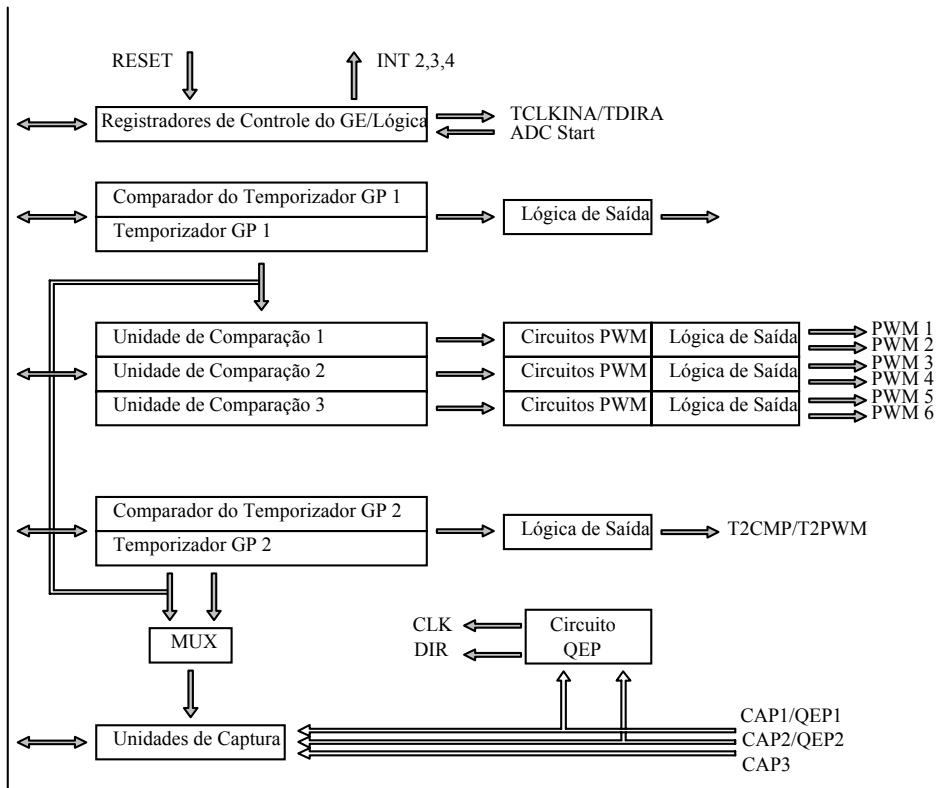

| 6.5   | Event Manager .....                                    | 102 |

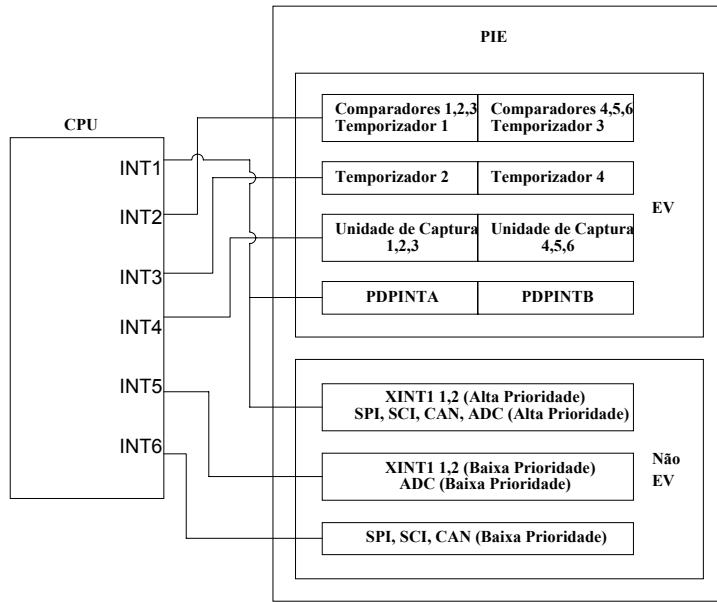

| 6.6   | Interrupção .....                                      | 104 |

| 6.7   | Representação Numérica em DSP .....                    | 106 |

| 6.7.1 | Processadores de Ponto Flutuante .....                 | 106 |

|                   |                                                    |     |

|-------------------|----------------------------------------------------|-----|

| 6.7.2             | Processadores de Ponto Fixo .....                  | 107 |

| 6.7.3             | Implementação do Programa .....                    | 108 |

| 6.8               | Conclusões.....                                    | 109 |

| <b>CAPITULO 7</b> |                                                    |     |

| 7                 | <b>RESULTADOS EXPERIMENTAIS.....</b>               | 110 |

| 7.1               | Introdução.....                                    | 110 |

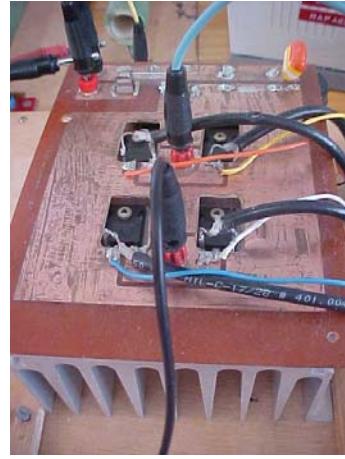

| 7.2               | Estrutura de Potência .....                        | 110 |

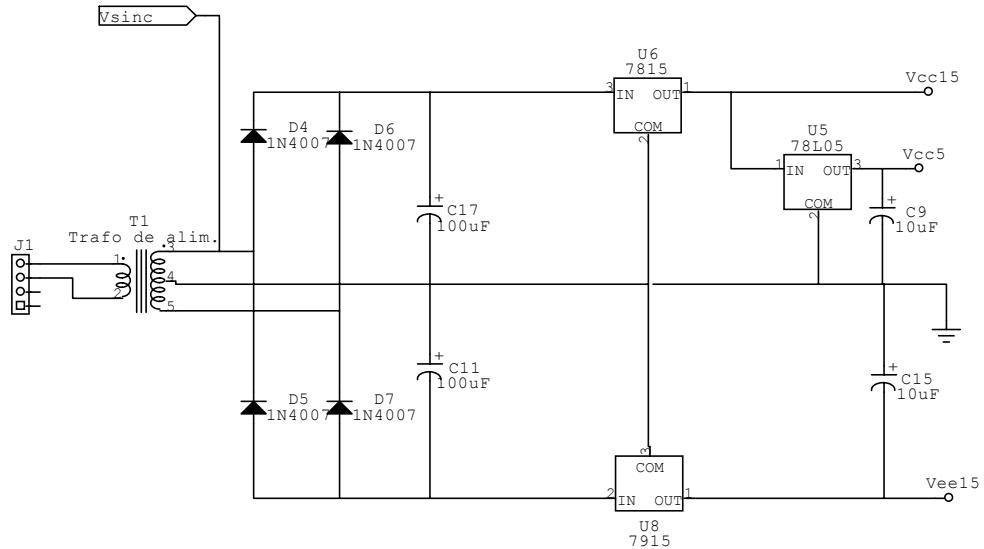

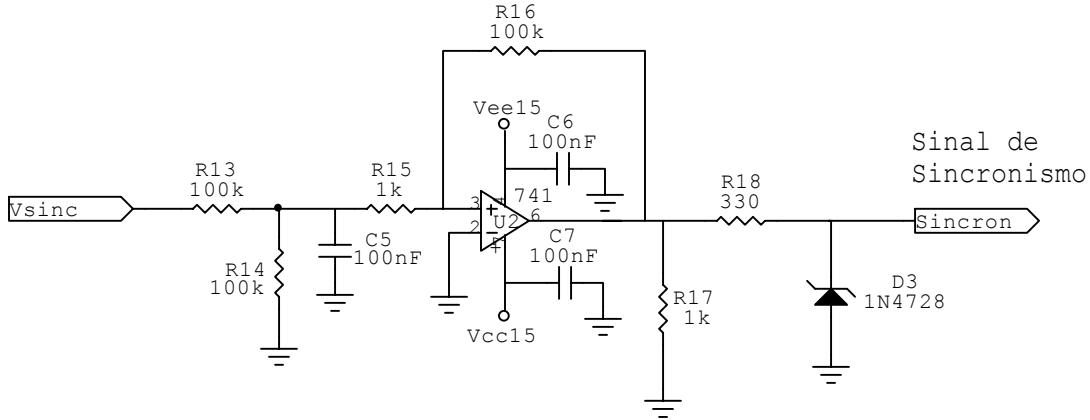

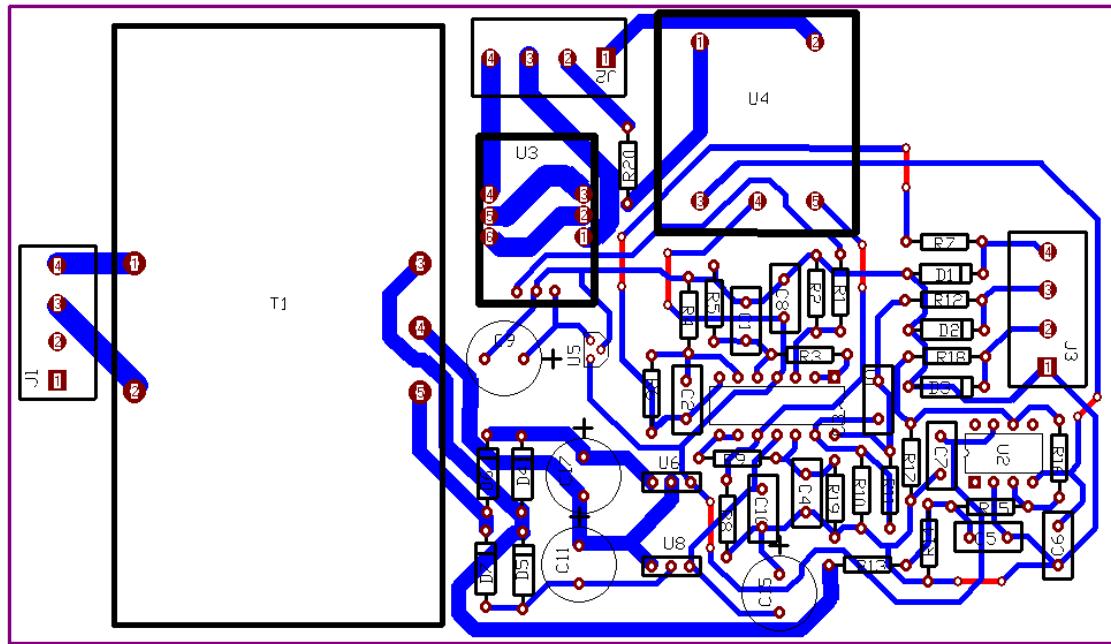

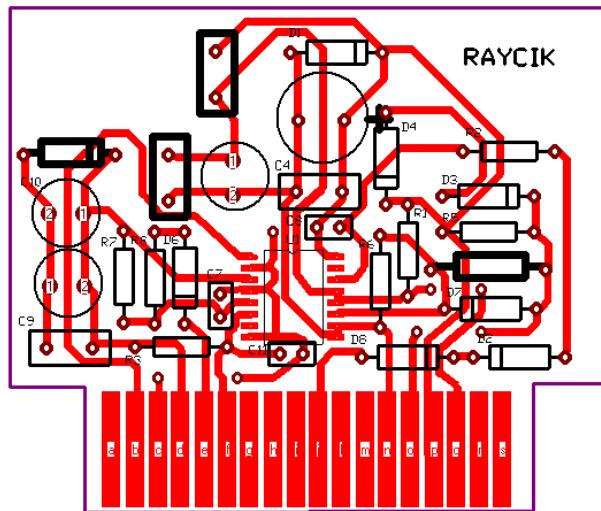

| 7.3               | Placa de Condicionamento de Sinais.....            | 111 |

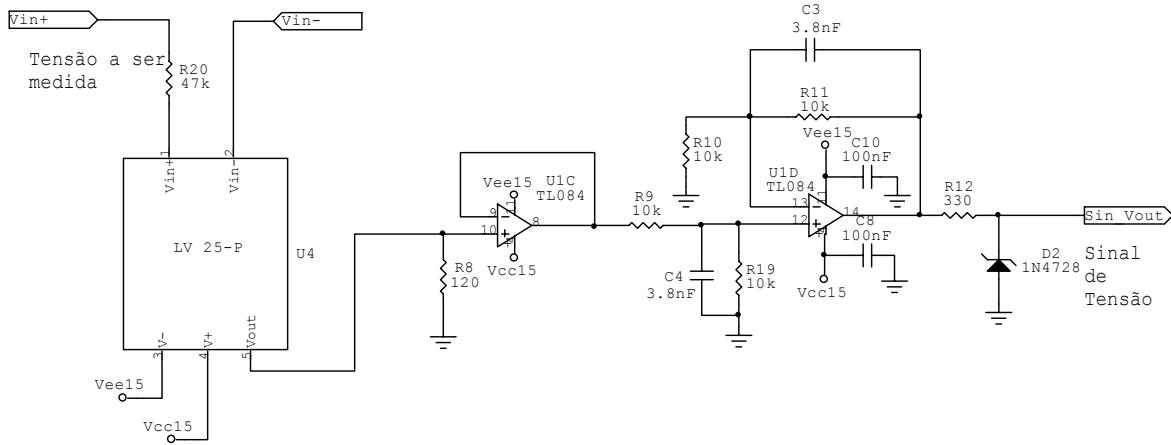

| 7.4               | Placa de Comando.....                              | 113 |

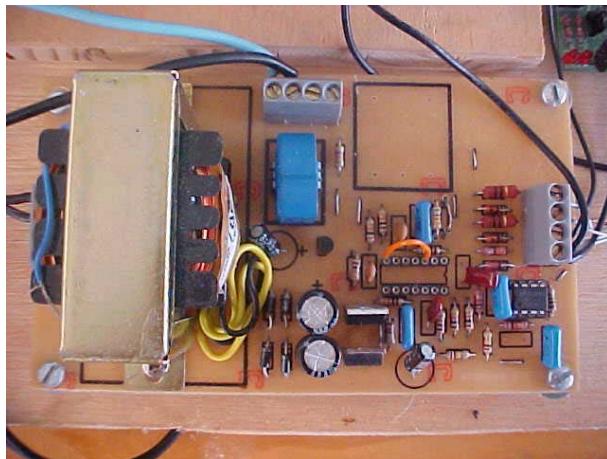

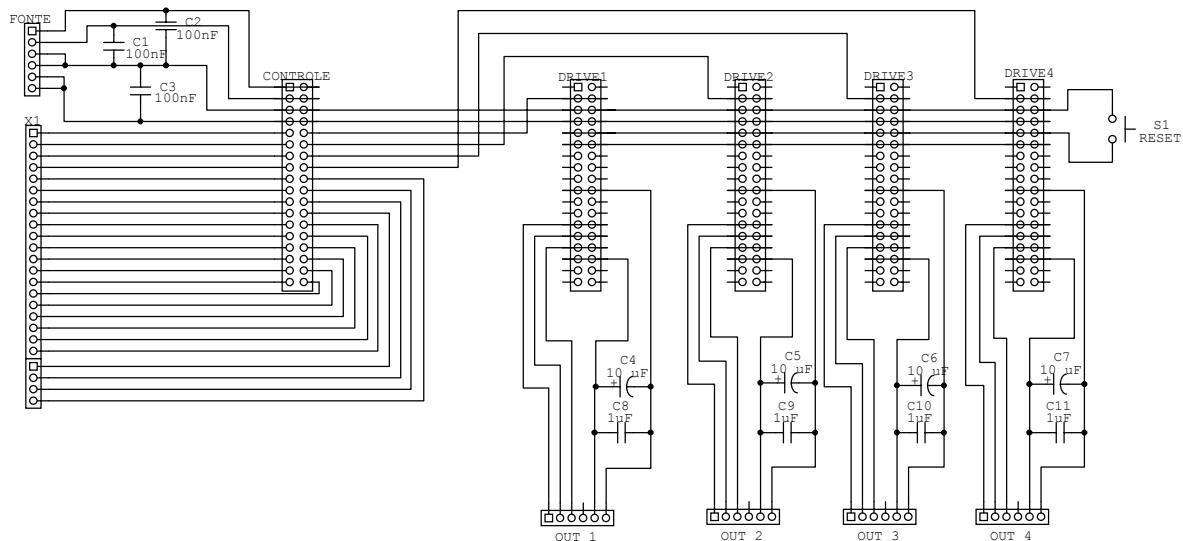

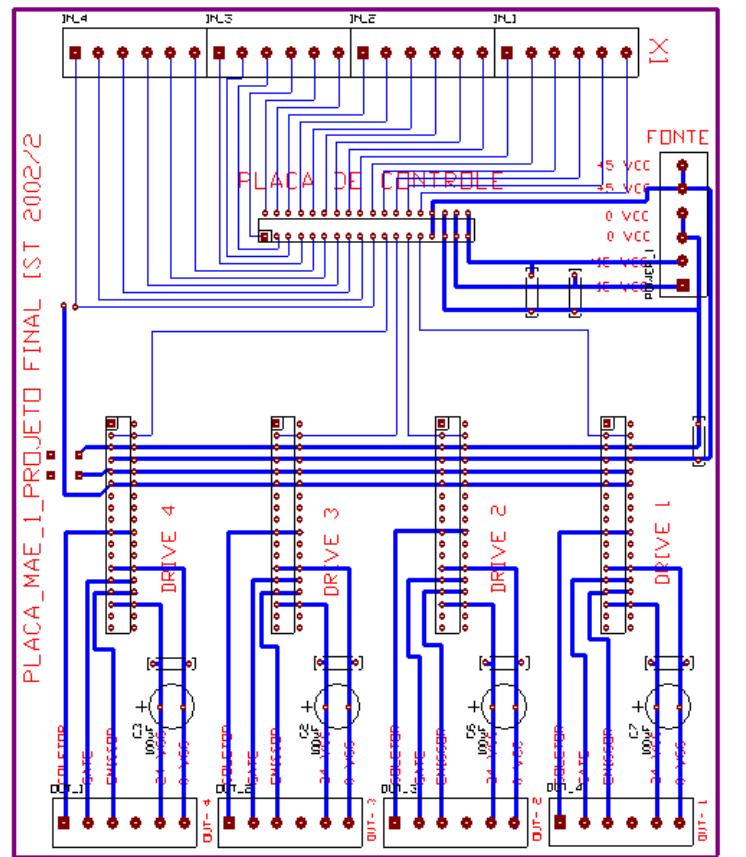

| 7.5               | Placa de Controle .....                            | 116 |

| 7.6               | Protótipo Final.....                               | 116 |

| 7.7               | Resultados Experimentais .....                     | 117 |

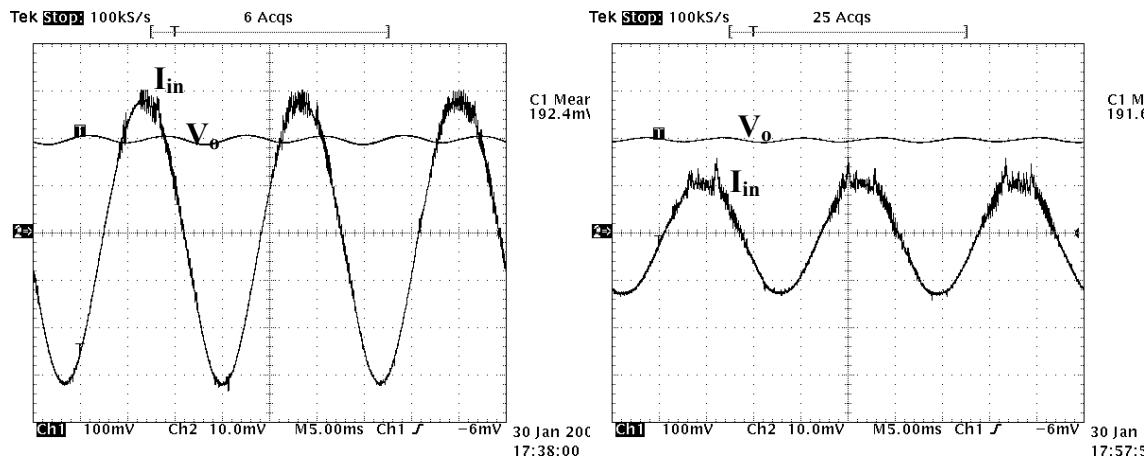

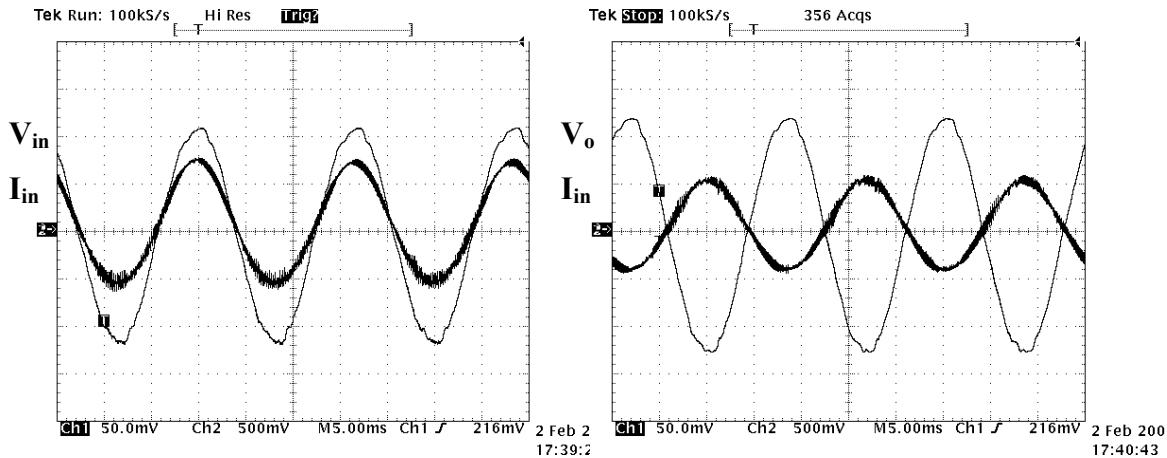

| 7.7.1             | Tensão e Corrente Drenada pela Rede.....           | 117 |

| 7.7.2             | Tensão e Corrente Drenada pela Rede.....           | 118 |

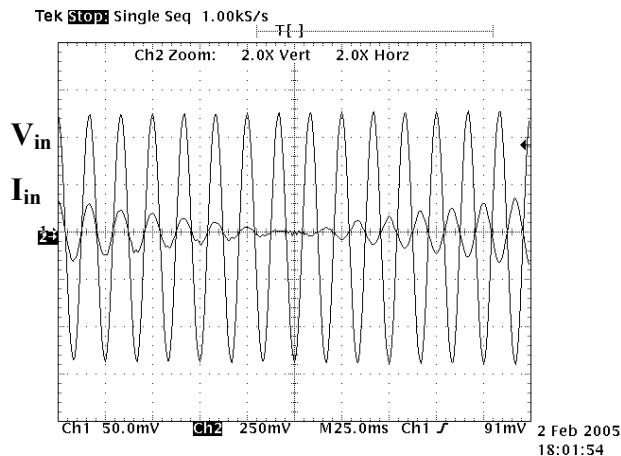

| 7.7.3             | Tensão e Corrente na Carga.....                    | 118 |

| 7.7.4             | Tensão na Carga e Corrente Drenada pela Rede ..... | 119 |

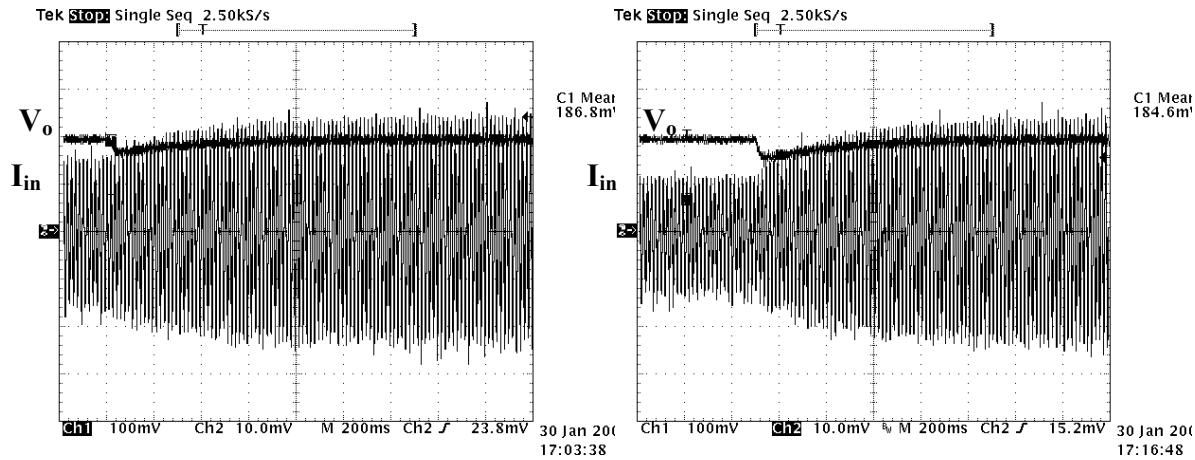

| 7.7.5             | Ensaio de Mudança de Carga.....                    | 119 |

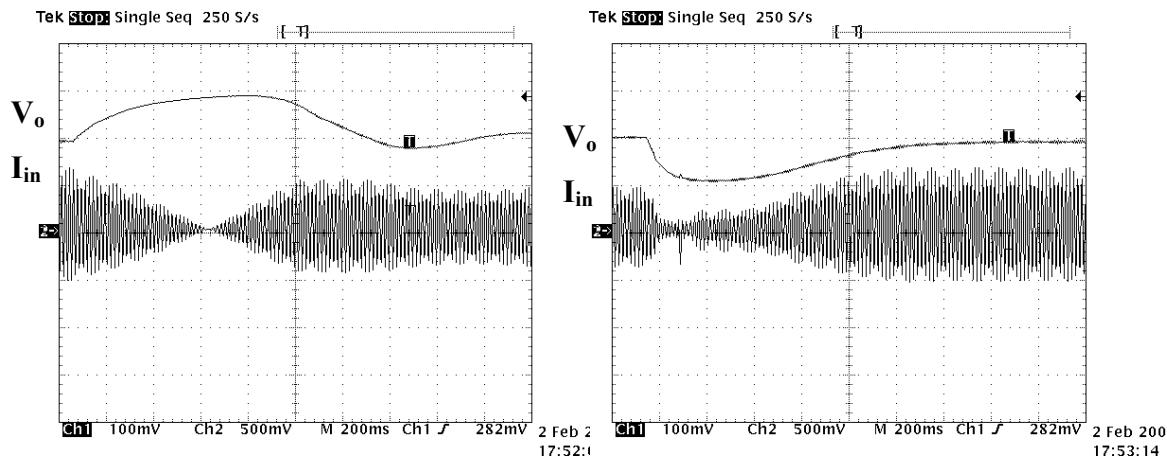

| 7.7.6             | Regeneração de Energia.....                        | 120 |

| 7.8               | Conclusões.....                                    | 122 |

| 8                 | <b>CONCLUSÕES GERAIS .....</b>                     | 123 |

| 9                 | <b>BIBLIOGRAFIA .....</b>                          | 124 |

| 10                | <b>ANEXO I – Programa do DSP .....</b>             | 126 |

| 11                | <b>ANEXO II – Layout da Placas .....</b>           | 131 |

| 11.1              | Placa de Aquisição .....                           | 131 |

| 11.2              | Placa dos Drives de Comando .....                  | 131 |

| 11.3              | Placa de Mãe para Drives de Comando .....          | 132 |

| 12                | <b>ANEXO II – Listas de Componentes .....</b>      | 133 |

## ÍNDICE DE FIGURAS

### CAPÍTULO 1

|                                                                                                    |           |

|----------------------------------------------------------------------------------------------------|-----------|

| <b>Figura 1-1 Conversor reversível de corrente monofásico.</b> .....                               | <b>1</b>  |

| <b>Figura 1-2 Conversor reversível de corrente monofásico.</b> .....                               | <b>2</b>  |

| <b>Figura 1-3 Estrutura representativa de um fonte de corrente .....</b>                           | <b>2</b>  |

| <b>Figura 1-4 Referência adotada para tensão e corrente positivas.....</b>                         | <b>3</b>  |

| <b>Figura 1-5 Representação dos quadrantes de operação.....</b>                                    | <b>3</b>  |

| <b>Figura 1-6 Comportamento das formas de onda para Retificador e Inversor.....</b>                | <b>4</b>  |

| <b>Figura 1-7 1<sup>a</sup> etapa de operação para 1º quadrante. ....</b>                          | <b>5</b>  |

| <b>Figura 1-8 2<sup>a</sup> etapa de operação para 1º quadrante. ....</b>                          | <b>6</b>  |

| <b>Figura 1-9 Tensão nas chaves e corrente e tensão no indutor de entrada (1º quadrante).....</b>  | <b>8</b>  |

| <b>Figura 1-10 1<sup>a</sup> etapa de operação para 3º quadrante. ....</b>                         | <b>9</b>  |

| <b>Figura 1-11 2<sup>a</sup> etapa de operação para 3º quadrante. ....</b>                         | <b>9</b>  |

| <b>Figura 1-12 Tensão nas chaves e corrente e tensão no indutor de entrada (3º quadrante).....</b> | <b>11</b> |

### CAPÍTULO 2

|                                                                                                           |           |

|-----------------------------------------------------------------------------------------------------------|-----------|

| <b>Figura 2-1 Processo de geração de sinal PWM. ....</b>                                                  | <b>14</b> |

| <b>Figura 2-2 Variação da razão cíclica em função de <math>\omega t</math> .....</b>                      | <b>16</b> |

| <b>Figura 2-3 Variação da Tensão entre os pontos <i>a</i> e <i>b</i> em função da razão cíclica. ....</b> | <b>17</b> |

| <b>Figura 2-4 Etapas do funcionamento para um período de chaveamento no 1º quadrante. ....</b>            | <b>22</b> |

| <b>Figura 2-5 Período de chaveamento para o 1º quadrante.....</b>                                         | <b>22</b> |

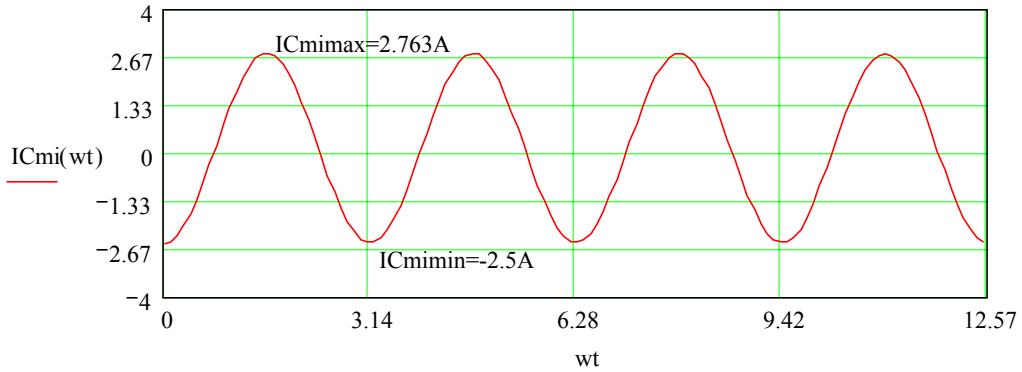

| <b>Figura 2-6 Corrente Media Instantânea no Capacitor.....</b>                                            | <b>24</b> |

| <b>Figura 2-7 1<sup>a</sup> etapa de operação para 1º quadrante. ....</b>                                 | <b>25</b> |

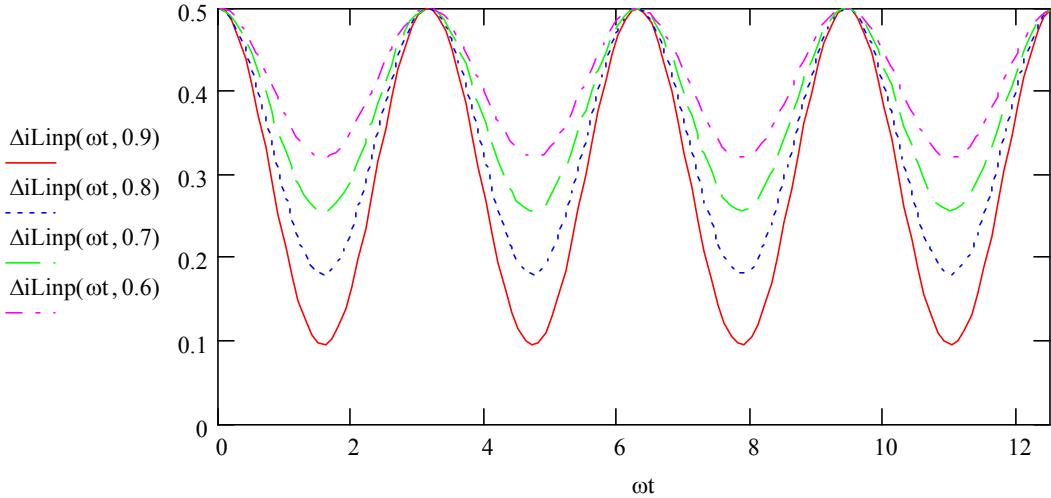

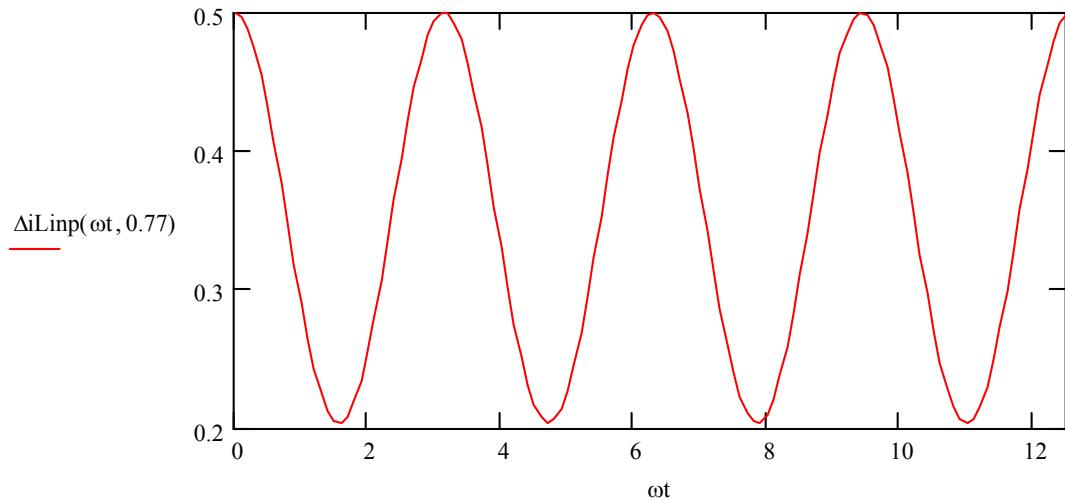

| <b>Figura 2-8 Ondulação de corrente parametrizada em função de <math>\omega t</math> .....</b>            | <b>27</b> |

| <b>Figura 2-9 Ondulação de corrente parametrizada para um período de funcionamento da rede.....</b>       | <b>27</b> |

### CAPÍTULO 3

|                                                                                               |           |

|-----------------------------------------------------------------------------------------------|-----------|

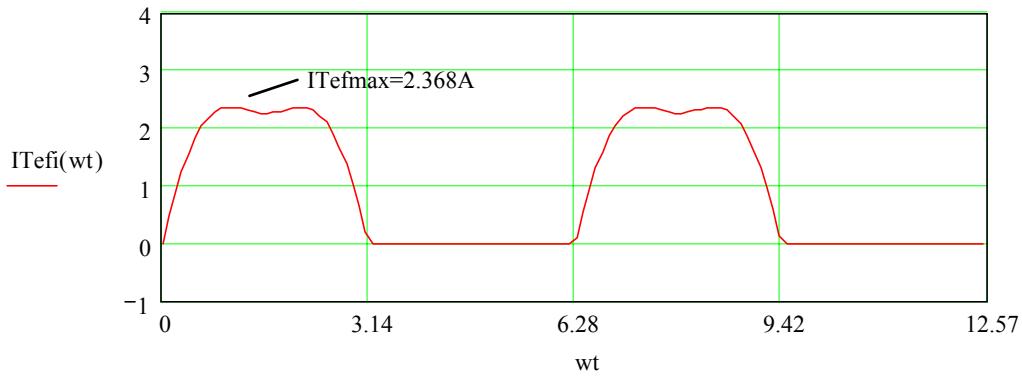

| <b>Figura 3-1 Variação da corrente no transistor em função de <math>\omega t</math> .....</b> | <b>37</b> |

| <b>Figura 3-2 Variação da corrente no diodo em função de <math>wt</math>.....</b>             | <b>38</b> |

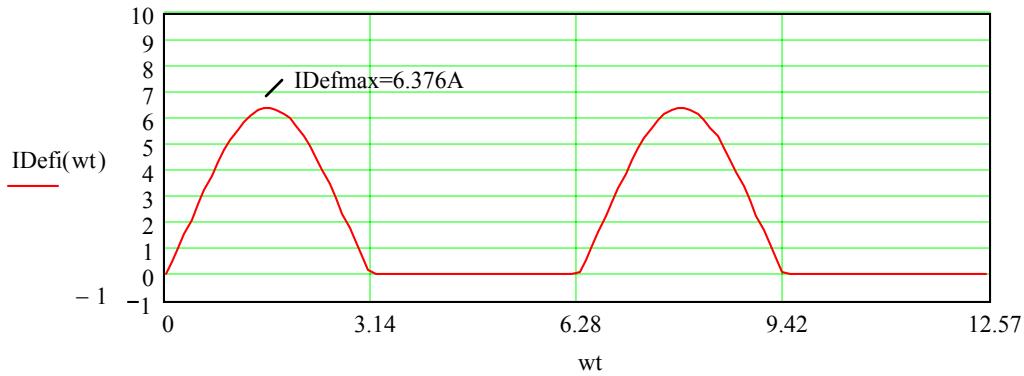

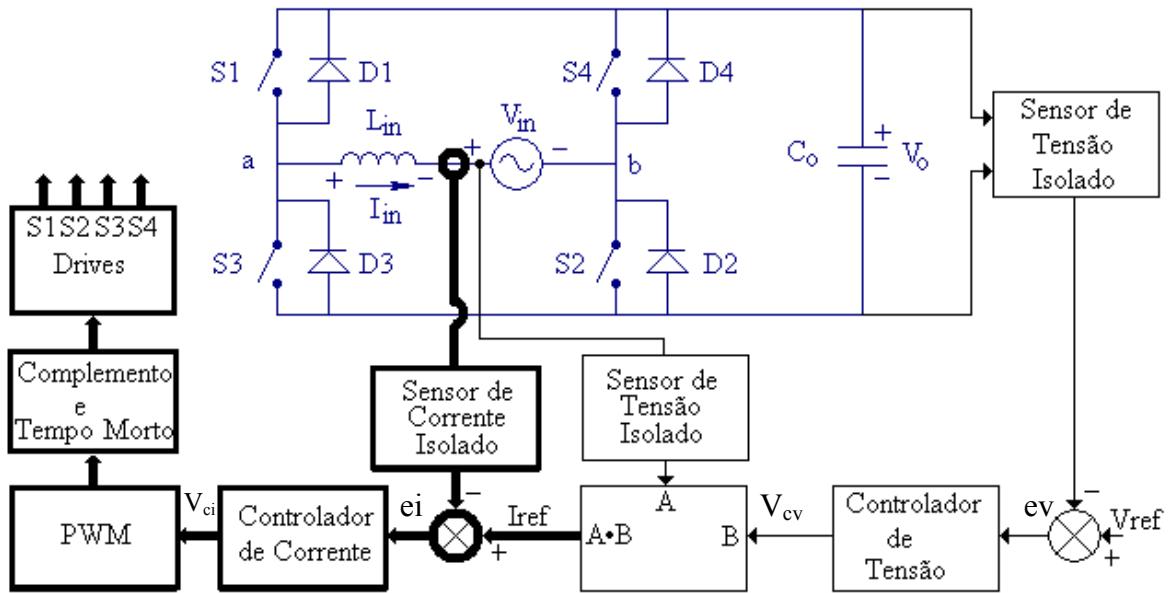

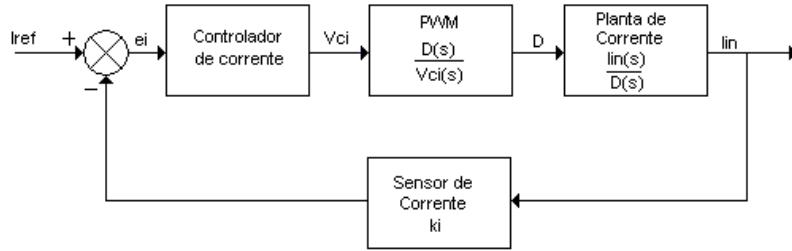

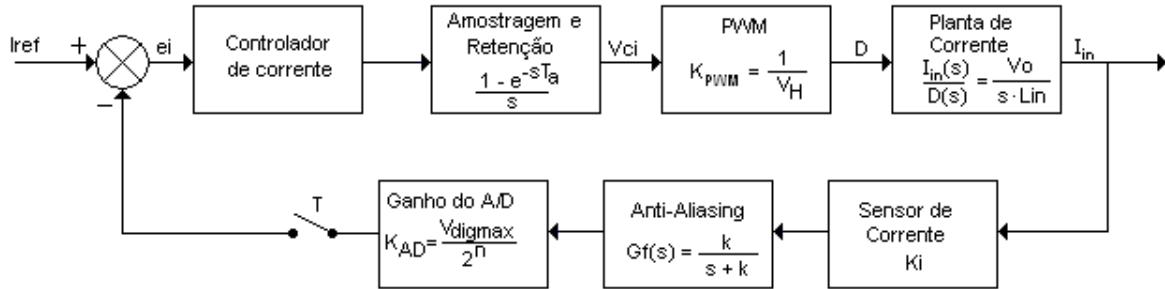

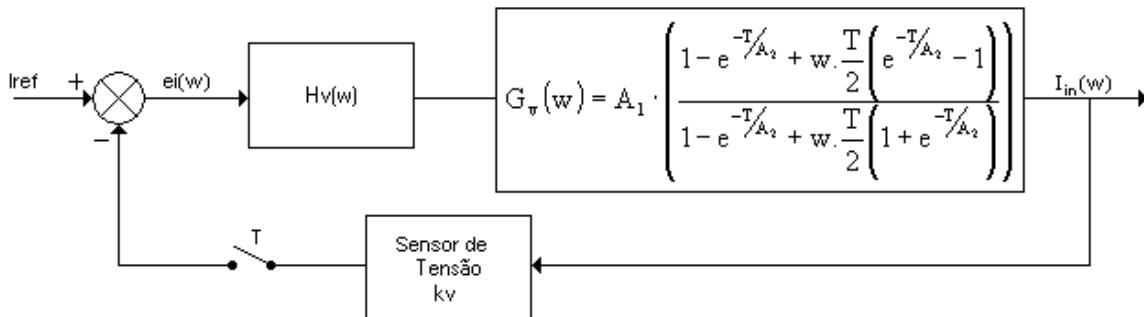

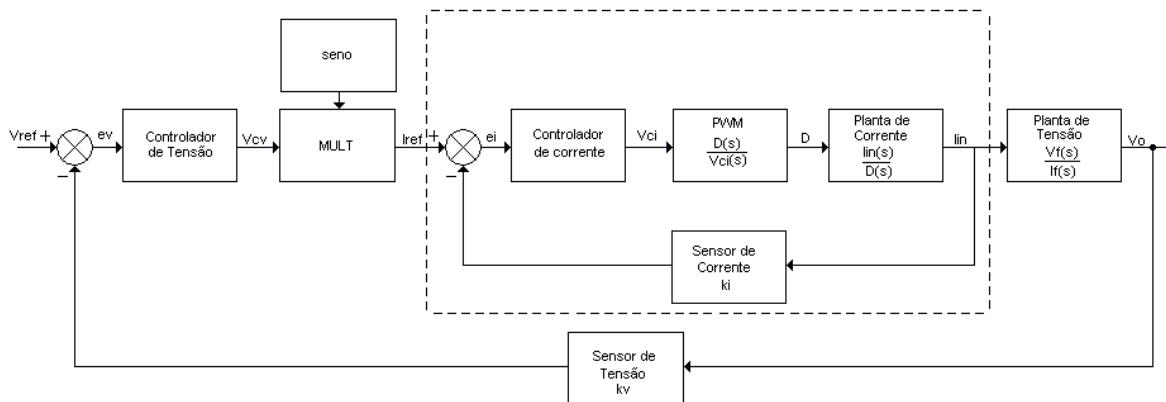

| <b>Figura 4-1 Diagrama de blocos do controle do Conversor(Malha de Corrente). ....</b>        | <b>45</b> |

| <b>Figura 4-2 Diagrama de blocos do controle da malha de corrente. ....</b>                   | <b>46</b> |

| <b>Figura 4-3 Diagrama de blocos do controle do Conversor(Malha de Tensão).....</b>           | <b>46</b> |

| <b>Figura 4-4 Diagrama de blocos do controle da malha de Tensão.....</b>                      | <b>47</b> |

| <b>Figura 4-5 Diagrama de blocos do controle da malha de Tensão.....</b>                      | <b>48</b> |

| <b>Figura 4-6 Diagrama de blocos do controle de um Conversor de Corrente.....</b>             | <b>49</b> |

| <b>Figura 4-7 Esquema do Conversor Reversível em corrente. ....</b>                           | <b>50</b> |

| <b>Figura 4-8 Modelo para grandes sinais. ....</b>                                            | <b>50</b> |

|                                                                                                                      |    |

|----------------------------------------------------------------------------------------------------------------------|----|

| <b>Figura 4-9</b> Circuito simplificado do conversor .....                                                           | 52 |

| <b>Figura 4-10</b> Efeito <i>anti-aliasing</i> .....                                                                 | 53 |

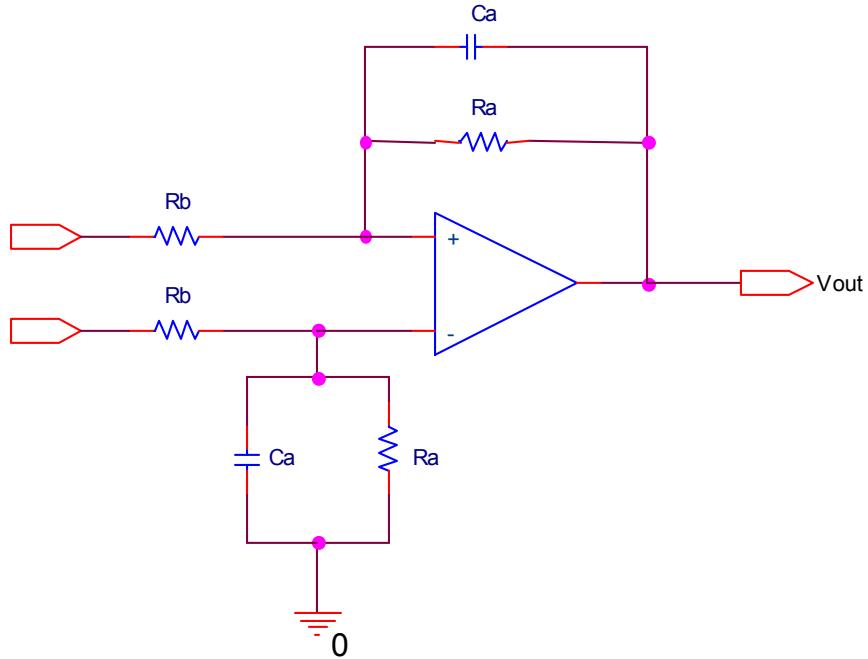

| <b>Figura 4-11</b> Diagrama esquemático do filtro de <i>anti-aliasing</i> .....                                      | 54 |

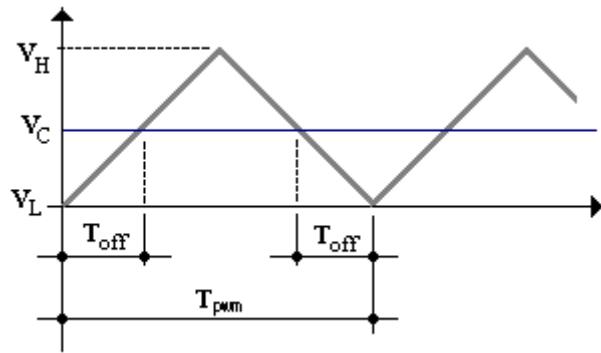

| <b>Figura 4-12</b> Forma de onda para geração do PWM.....                                                            | 55 |

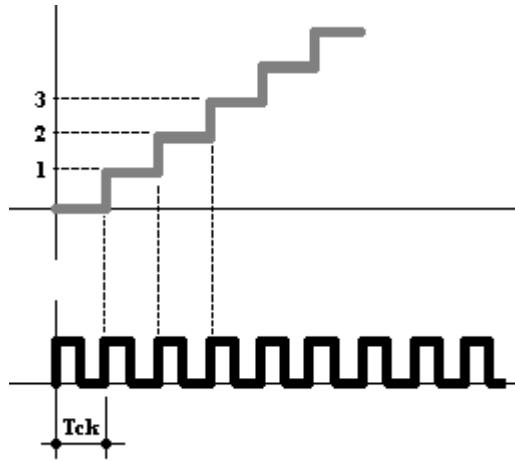

| <b>Figura 4-13</b> Valor da onda triangular sendo incrementada a cada período do clock. ....                         | 56 |

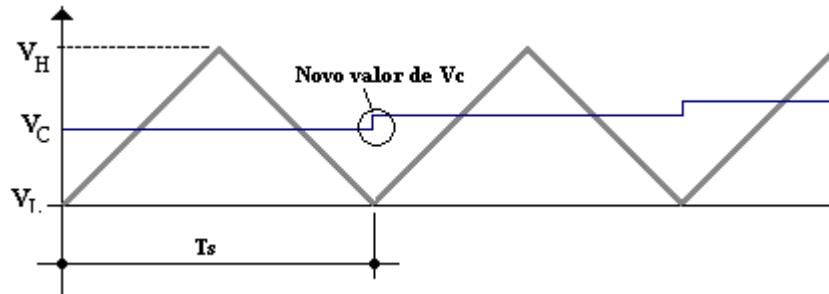

| <b>Figura 4-14</b> Valor de $V_c$ sendo atualizado a cada período $T_{pwm}$ .....                                    | 56 |

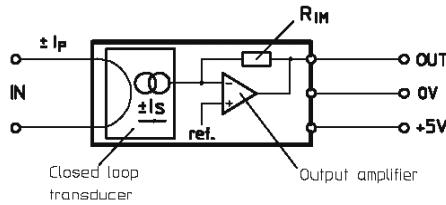

| <b>Figura 4-15</b> Diagrama esquemático do Sensor de Corrente .....                                                  | 58 |

| <b>Figura 4-16</b> Relação entre corrente de fundo de escala e tensão de entrada.....                                | 58 |

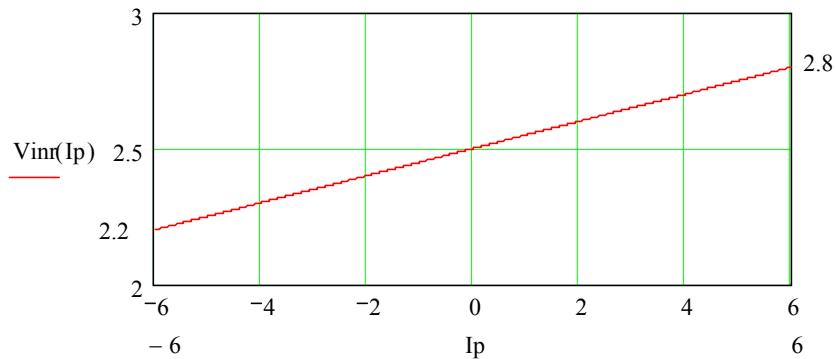

| <b>Figura 4-17</b> Diagrama de blocos do processo no domínio de $s$ e convertido para o domínio de $z$ .....         | 60 |

| <b>Figura 4-18</b> Mapeamento usando a transformação bilinear.....                                                   | 61 |

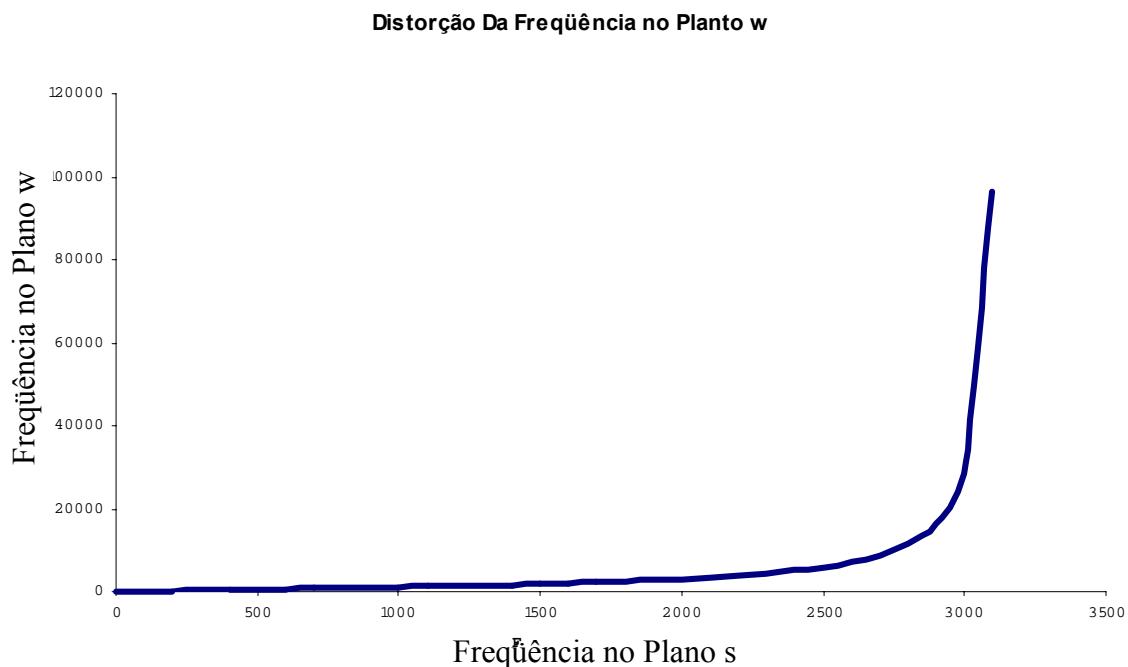

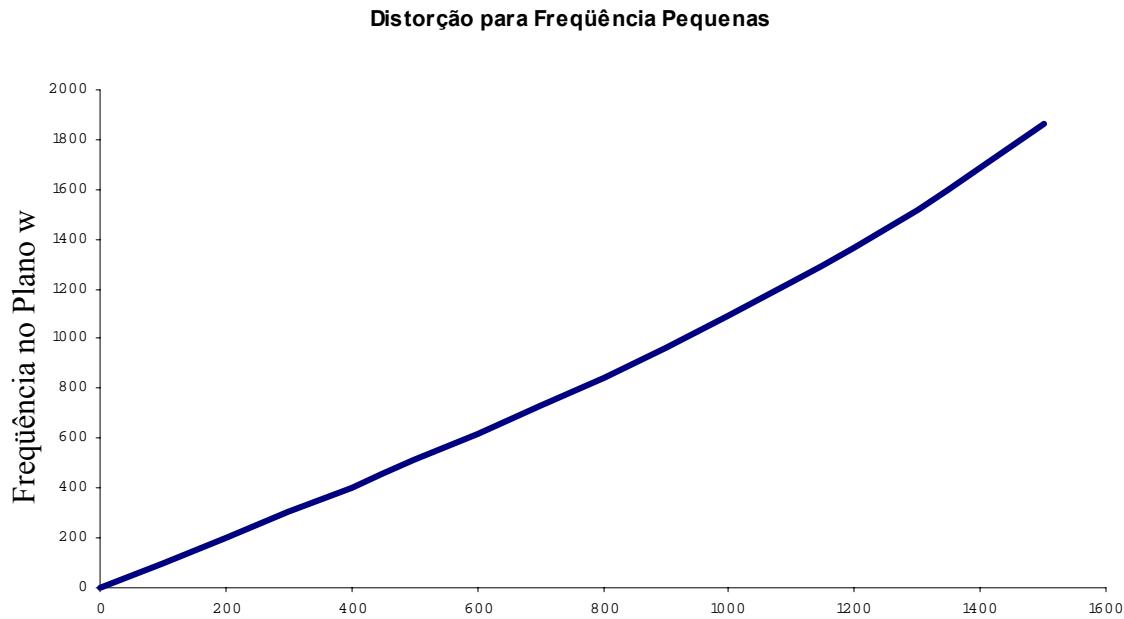

| <b>Figura 4-19</b> Distorção na freqüência devido ao mapeamento usando a transformação bilinear, com $T_a=1ms$ ..... | 62 |

| <b>Figura 4-20</b> Distorção menor para freqüência pequenas, com $T_a=1ms$ .....                                     | 63 |

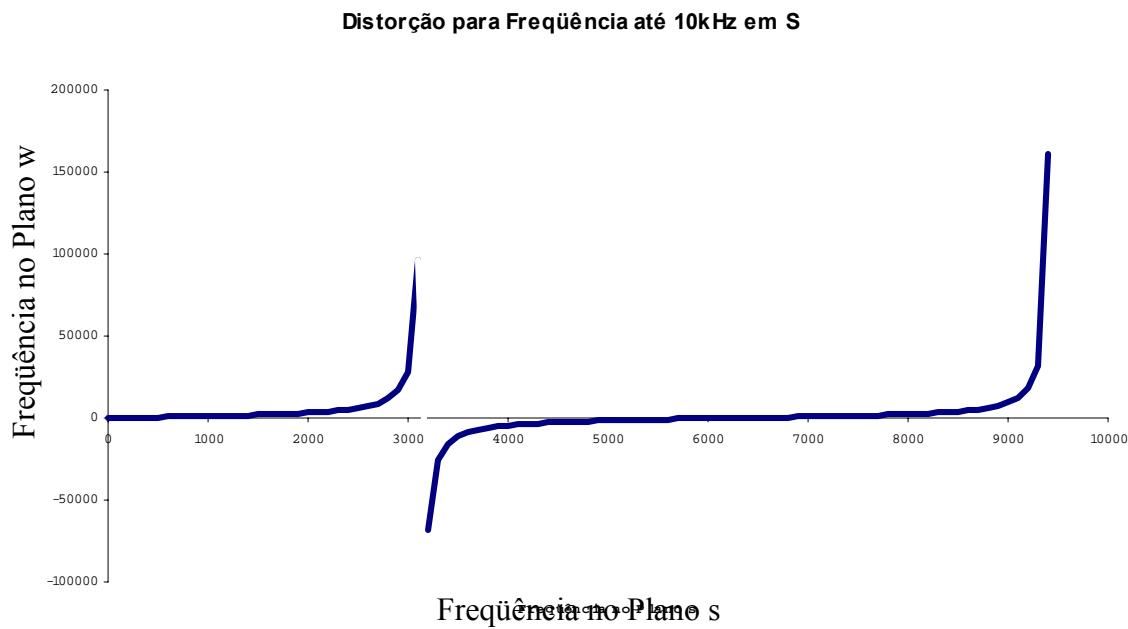

| <b>Figura 4-21</b> Distorção para freqüência no plano $s$ até 10kHz, com $T_a=1ms$ .....                             | 63 |

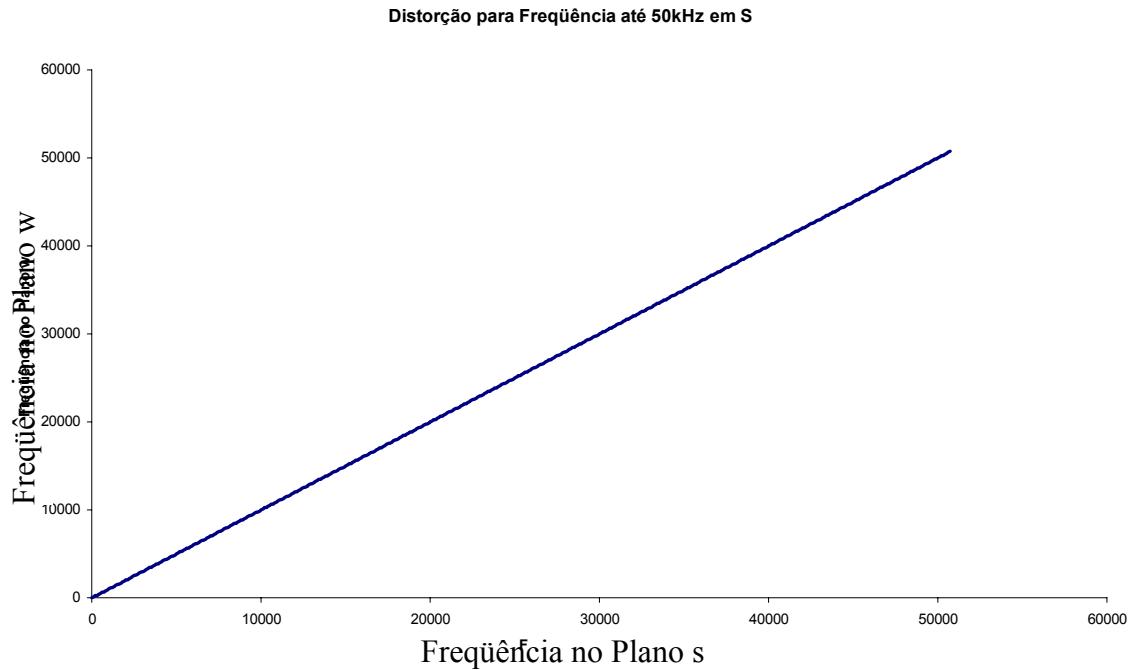

| <b>Figura 4-22</b> Distorção para freqüência no plano $s$ até 50kHz, com $T_a=1us$ .....                             | 64 |

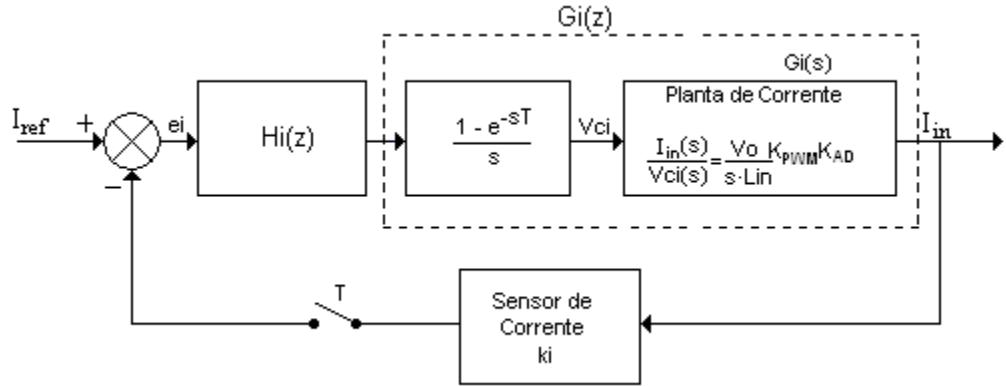

| <b>Figura 4-23</b> Malha de Controle da corrente com funções de transferência. ....                                  | 66 |

| <b>Figura 4-24</b> Malha de Controle da Corrente Simplificada.....                                                   | 67 |

| <b>Figura 4-25</b> Malha de Controle da Corrente Simplificada .....                                                  | 68 |

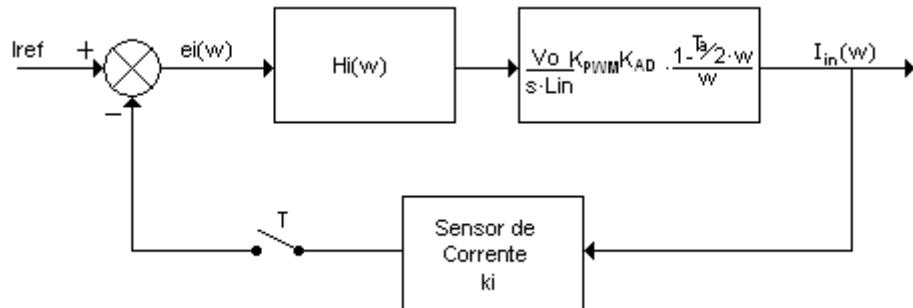

| <b>Figura 4-26</b> Resposta em freqüência para a planta de corrente continua e discreta.....                         | 71 |

| <b>Figura 4-27</b> Resposta da $FTMA_i$ com o controlador de corrente .....                                          | 73 |

| <b>Figura 4-28</b> Representação do bloco do controlador de corrente isoladamente .....                              | 74 |

| <b>Figura 4-29</b> Malha de controle de tensão .....                                                                 | 75 |

| <b>Figura 4-30</b> Malha de controle de tensão simplificada.....                                                     | 76 |

| <b>Figura 4-31</b> Malha de Controle de Tensão Simplificada.....                                                     | 78 |

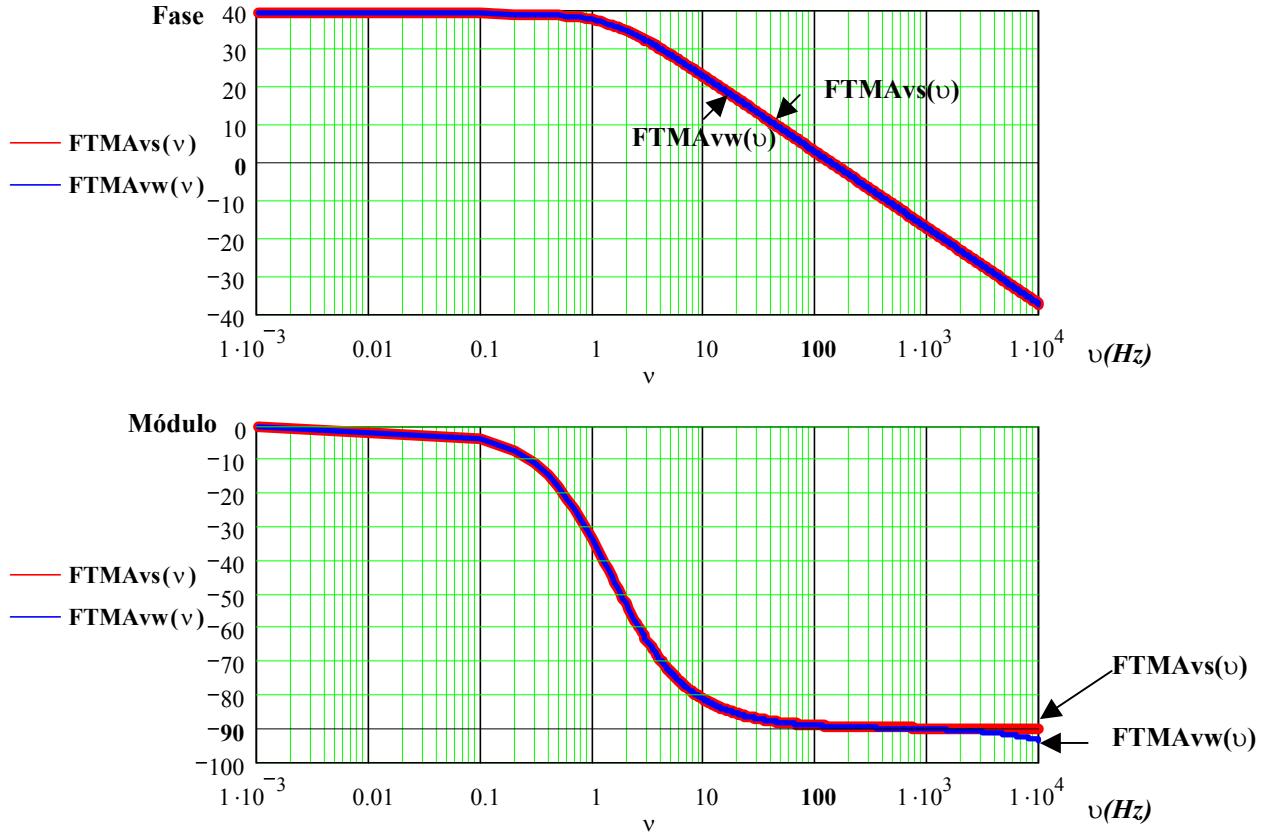

| <b>Figura 4-32</b> Resposta em freqüência para a planta de tensão contínua e discreta. ....                          | 82 |

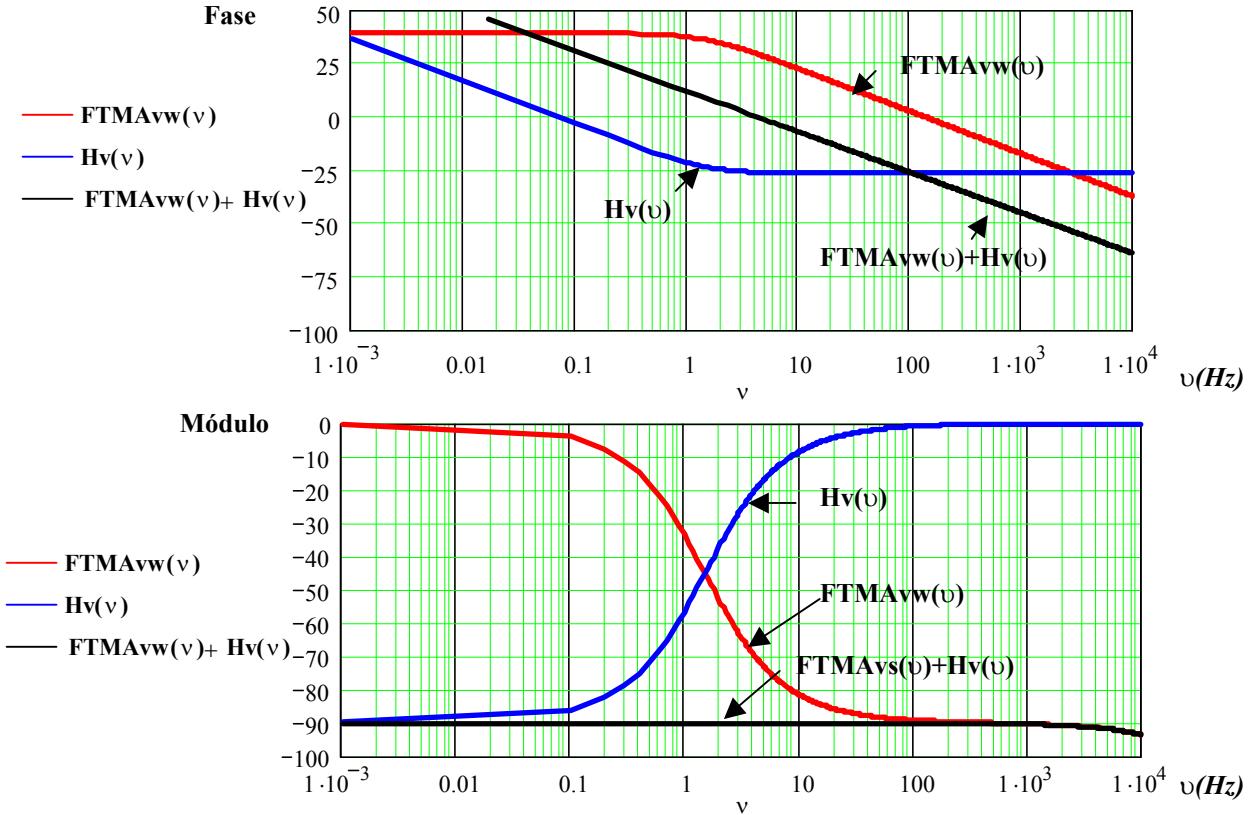

| <b>Figura 4-33</b> Resposta da $FTMA_i$ com o controlador de corrente .....                                          | 84 |

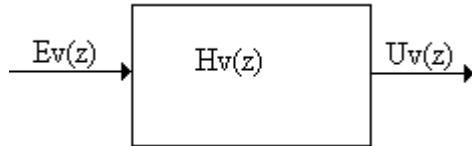

| <b>Figura 4-34</b> Representação do bloco do controlador de tensão isoladamente.....                                 | 85 |

## CAPÍTULO 5

|                                                                                          |    |

|------------------------------------------------------------------------------------------|----|

| <b>Figura 5-1</b> Diagrama de blocos genérico .....                                      | 86 |

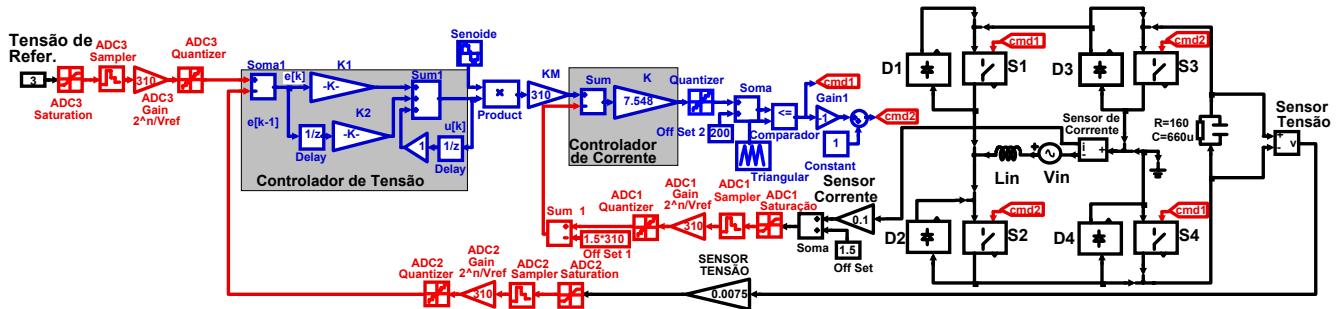

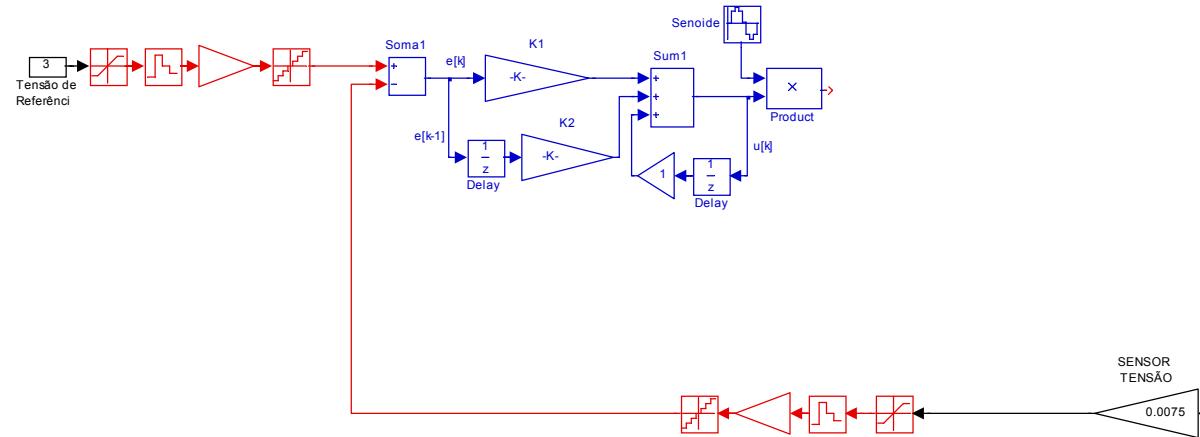

| <b>Figura 5-2</b> Diagrama de blocos do controle do conversor usado para simulação.....  | 87 |

| <b>Figura 5-3</b> Diagrama da malha de tensão.....                                       | 87 |

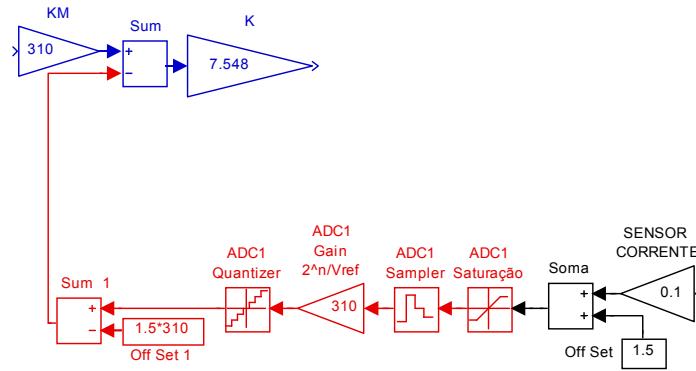

| <b>Figura 5-4</b> Diagrama de blocos utilizados na malha de corrente. ....               | 88 |

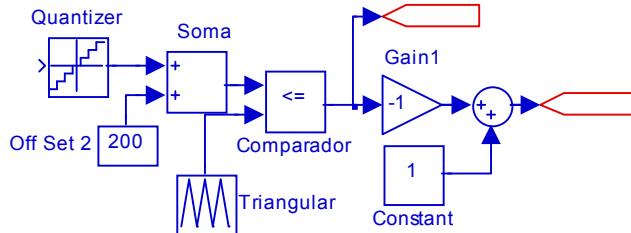

| <b>Figura 5-5</b> Diagrama de blocos para geração da onda PWM.....                       | 88 |

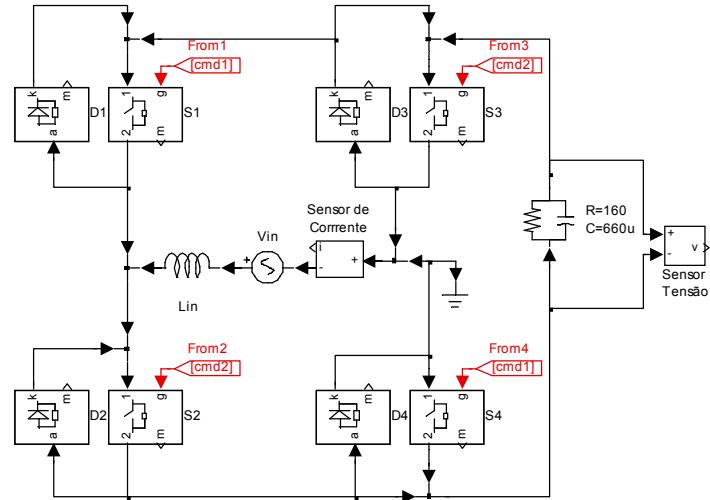

| <b>Figura 5-6</b> Estrutura de Potência.....                                             | 89 |

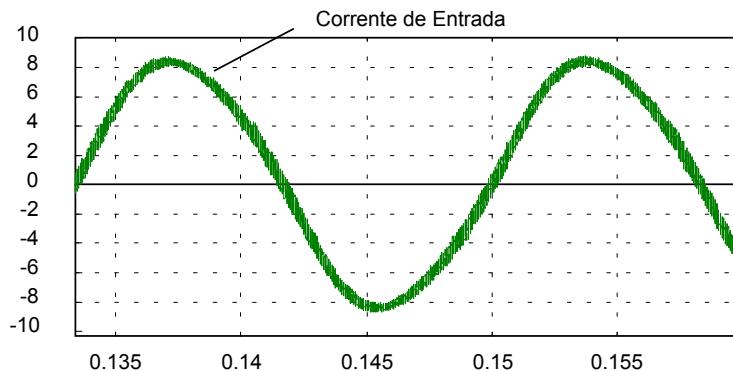

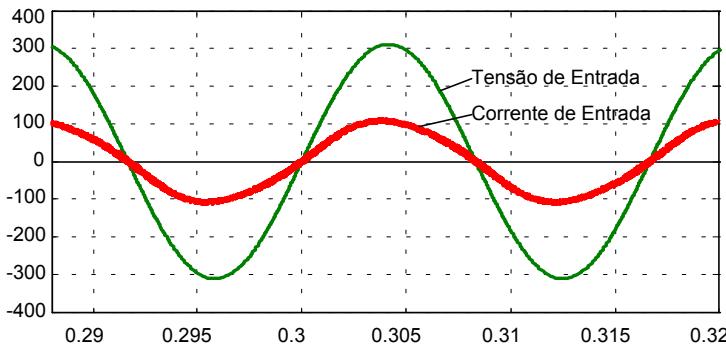

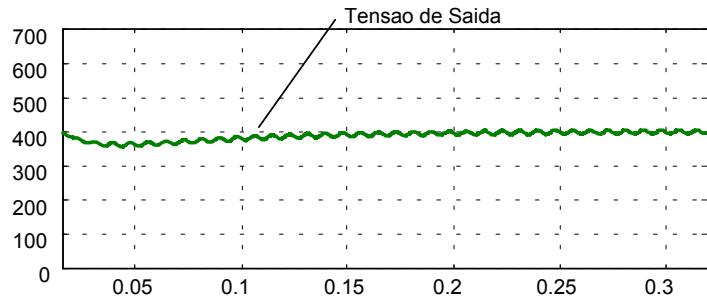

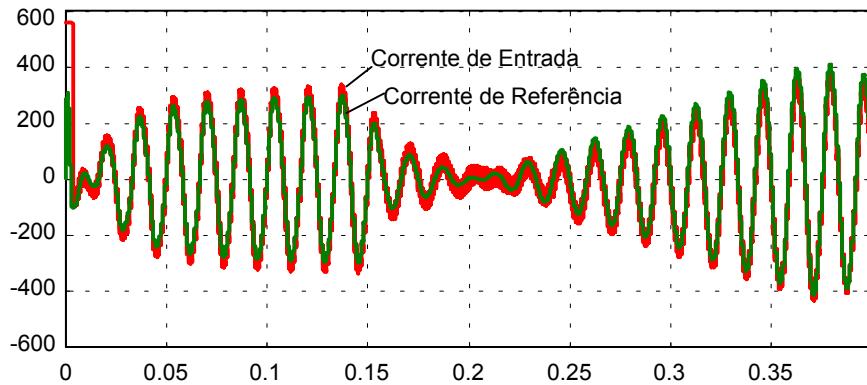

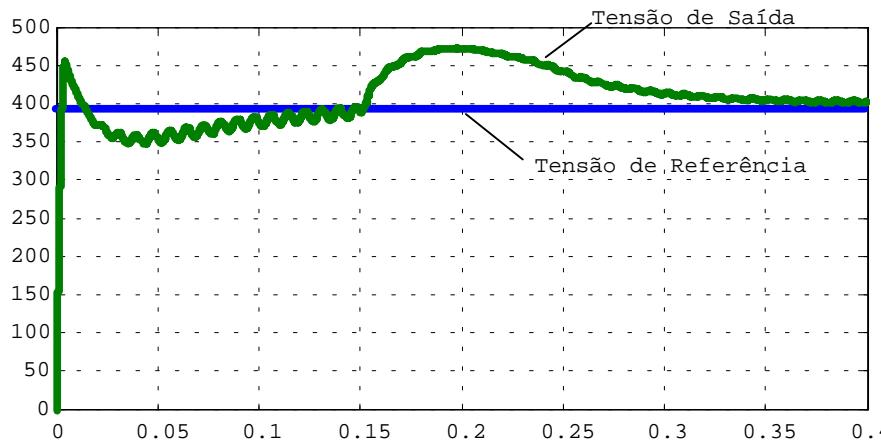

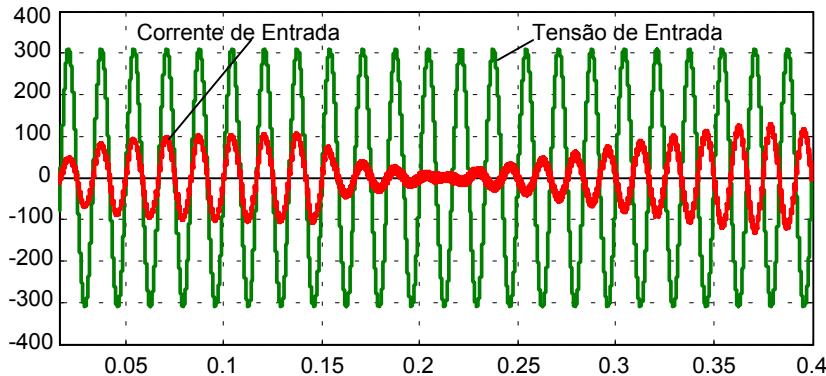

| <b>Figura 5-7</b> Formato Senoidal Imposto à Corrente de Entrada. ....                   | 89 |

| <b>Figura 5-8</b> Comparação entre a Corrente de Referência e a Corrente de Entrada..... | 90 |

| <b>Figura 5-9</b> Fase entre Tensão e Corrente de Entrada. ....                          | 90 |

| <b>Figura 5-10</b> Tensão de Saída. ....                                                 | 91 |

|                                                                                                  |    |

|--------------------------------------------------------------------------------------------------|----|

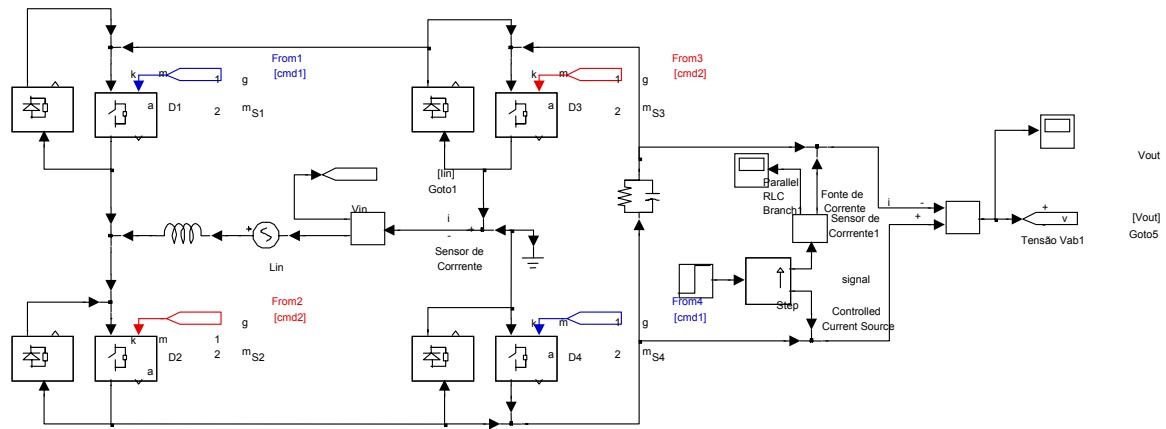

| <b>Figura 5-11</b> Estrutura para trabalhar com regeneração. ....                                | 92 |

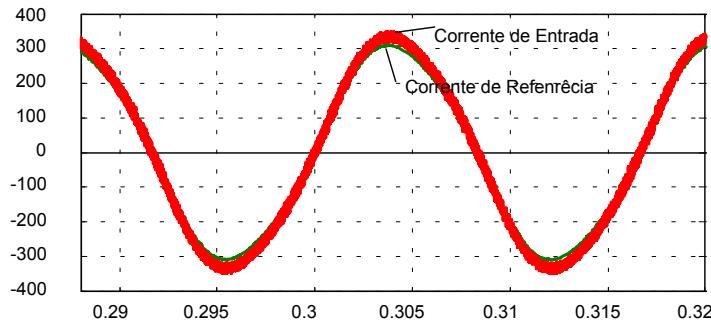

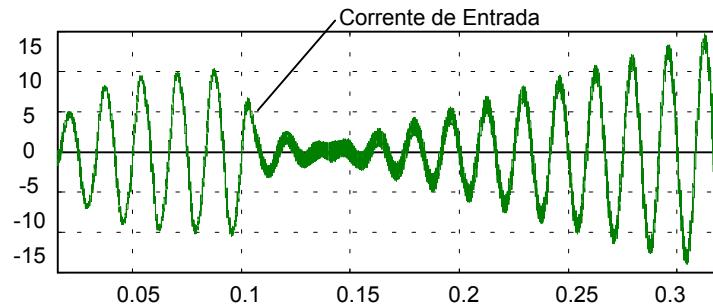

| <b>Figura 5-12</b> Efeito na corrente de entrada quando na regeneração de energia. ....          | 92 |

| <b>Figura 5-13</b> Corrente de entrada e corrente de referência dentro do DSP. ....              | 93 |

| <b>Figura 5-14</b> Comparação entre Tensão de Referência e Tensão de Entrada dentro do DSP. .... | 93 |

| <b>Figura 5-15</b> Comparação entre a fase da Tensão e Corrente de Entrada. ....                 | 94 |

## CAPÍTULO 6

|                                                                     |     |

|---------------------------------------------------------------------|-----|

| <b>Figura 6-1</b> Arquitetura esquemática do DSP TMS320LF24xx. .... | 98  |

| <b>Figura 6-2</b> Arquitetura esquemática do módulo ADC. ....       | 102 |

| <b>Figura 6-3</b> Arquitetura esquemática do EVA ....               | 103 |

| <b>Figura 6-4</b> Esquema de interrupção ....                       | 105 |

## CAPÍTULO 7

|                                                                                                                                          |     |

|------------------------------------------------------------------------------------------------------------------------------------------|-----|

| <b>Figura 7-1</b> Diagrama esquemático do circuito de potência do conversor.....                                                         | 110 |

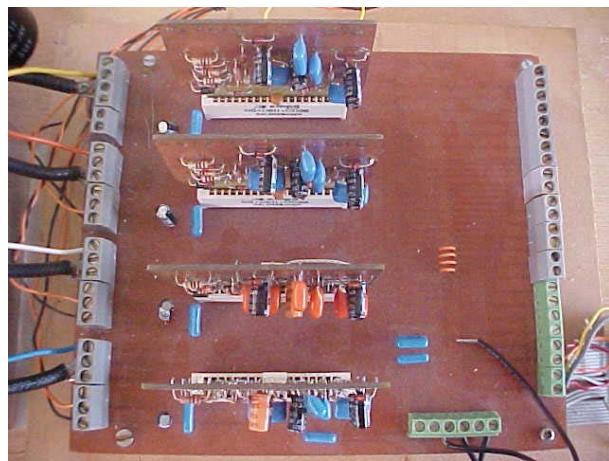

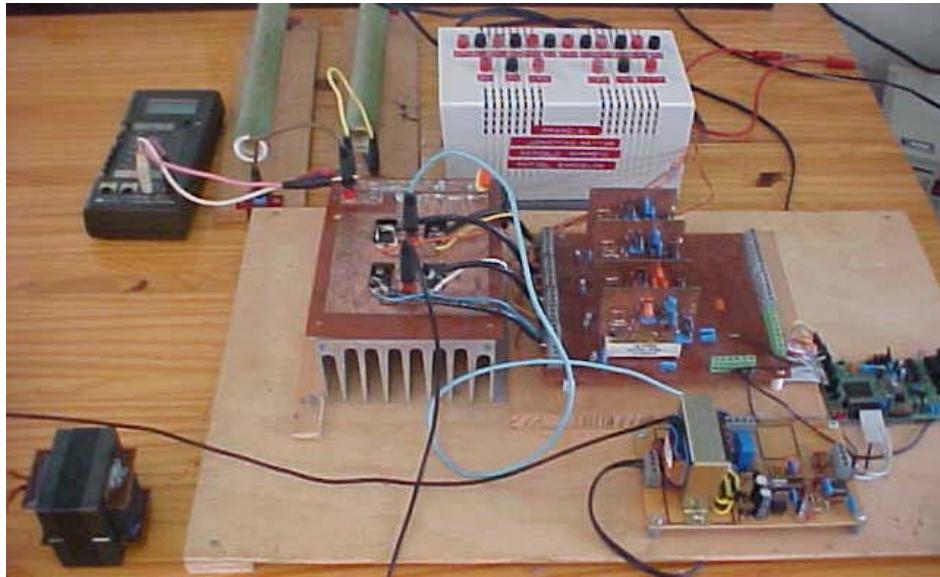

| <b>Figura 7-2</b> Aspecto final do circuito de potência. ....                                                                            | 111 |

| <b>Figura 7-3</b> Diagrama esquemático da fonte de alimentação da placa de aquisição. ....                                               | 111 |

| <b>Figura 7-4</b> Diagrama esquemático do circuito de sincronismo. ....                                                                  | 112 |

| <b>Figura 7-5</b> Diagrama esquemático do circuito de aquisição de corrente. ....                                                        | 112 |

| <b>Figura 7-6</b> Diagrama esquemático do circuito de aquisição de tensão de saída.....                                                  | 113 |

| <b>Figura 7-7</b> Aspecto final da placa de aquisição de dados. ....                                                                     | 113 |

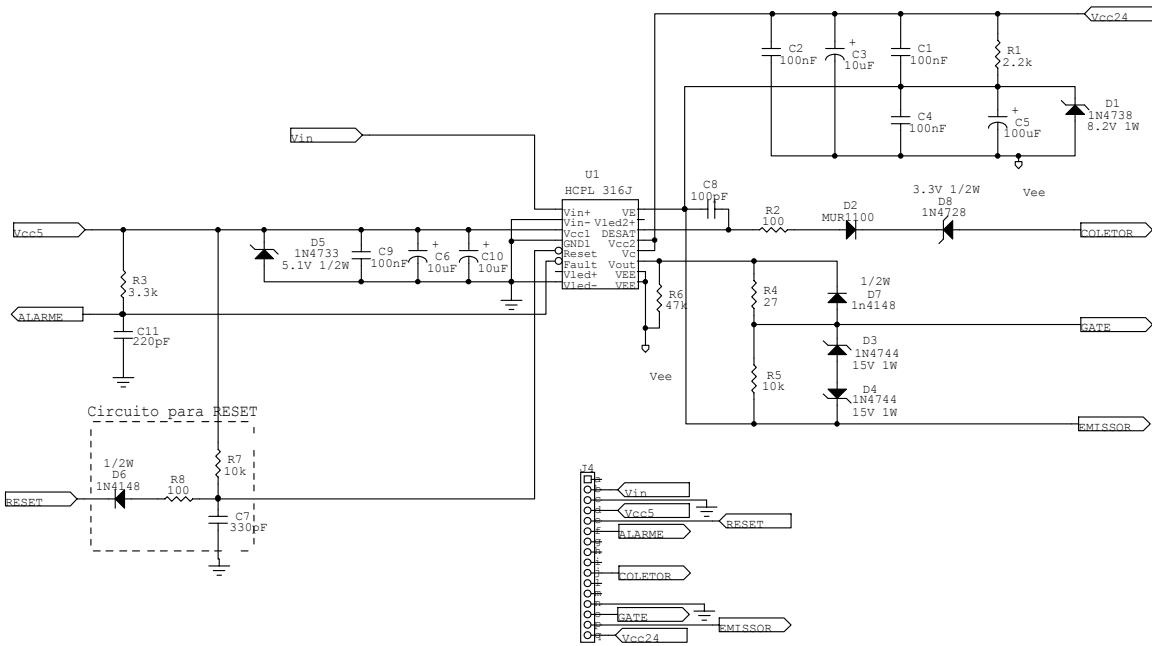

| <b>Figura 7-8</b> Diagrama esquemático da placa mãe.....                                                                                 | 114 |

| <b>Figura 7-9</b> Diagrama esquemático da placa mãe.....                                                                                 | 114 |

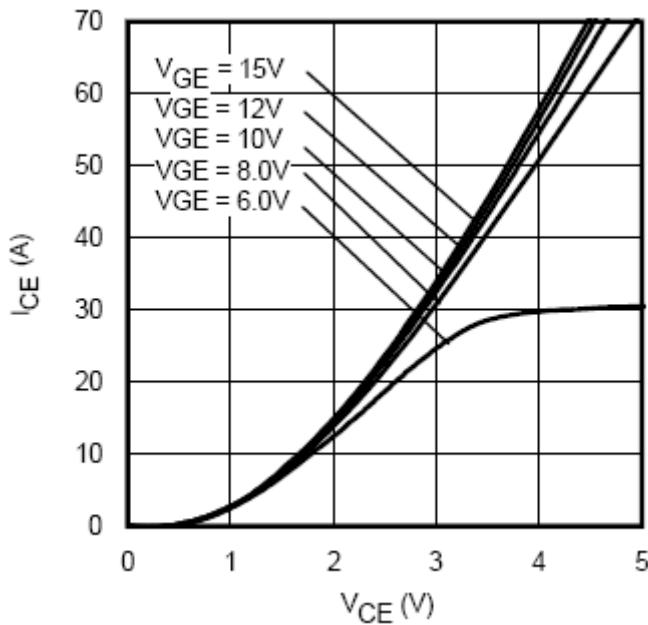

| <b>Figura 7-10</b> Característica de condução do IGBT IRGP35B60PD (Vce x Ic). Dados importantes para o dimensionamento da proteção. .... | 115 |

| <b>Figura 7-11</b> Aspecto final da placa de comando. ....                                                                               | 116 |

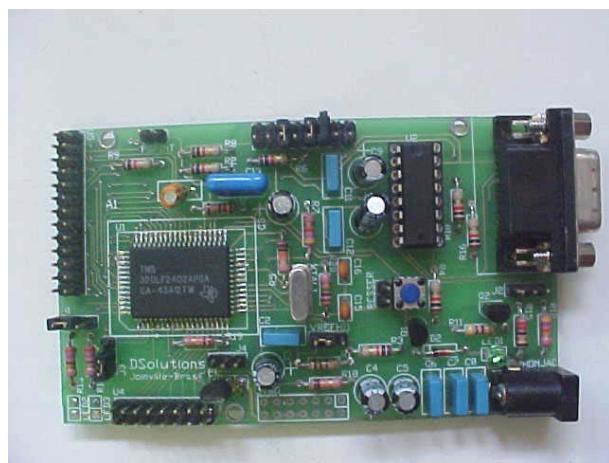

| <b>Figura 7-12</b> Aspecto final da placa de controle.....                                                                               | 116 |

| <b>Figura 7-13</b> Aspecto final do conversor com todos os módulos. ....                                                                 | 117 |

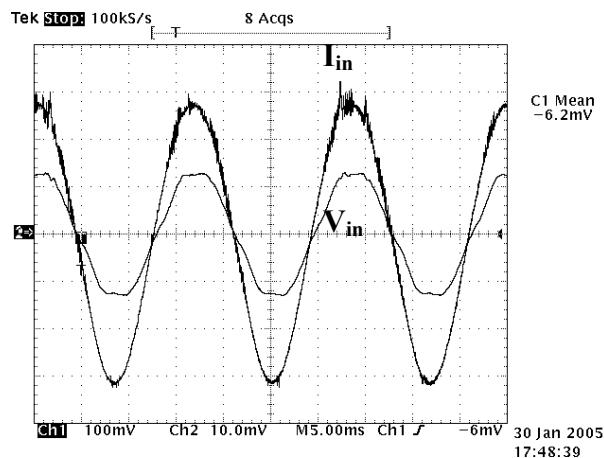

| <b>Figura 7-14</b> Formas de ondas de tensão e corrente drenada pela rede.....                                                           | 117 |

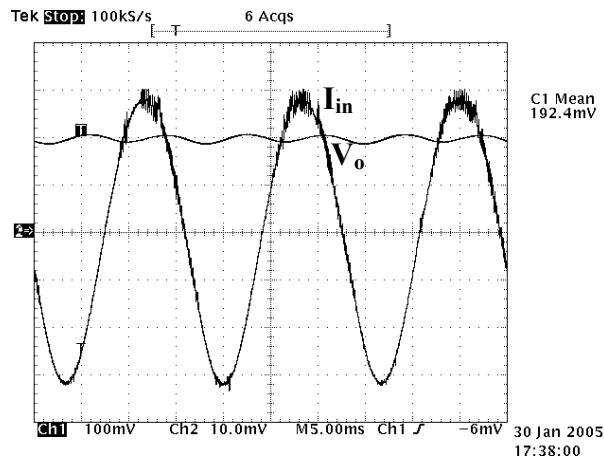

| <b>Figura 7-15</b> Formas de ondas de corrente drenada pela rede e tensão de saída.....                                                  | 118 |

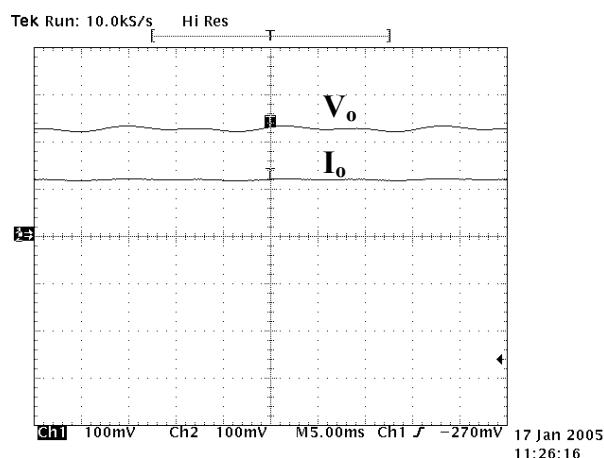

| <b>Figura 7-16</b> Formas de ondas de corrente e tensão de saída do conversor.....                                                       | 118 |

| <b>Figura 7-17</b> (a) controle não atuando sobre o conversor e (b) controle atuando sobre o conversor. ....                             | 119 |

| <b>Figura 7-18</b> (a) Degrau de 25% da aumento de carga. (b) Degrau de 50% de aumento de carga .....                                    | 120 |

| <b>Figura 7-19</b> Passagem do conversor para o modo de regeneração de energia. ....                                                     | 120 |

## ANEXO II

|                                                                                                  |     |

|--------------------------------------------------------------------------------------------------|-----|

| <b>Figura 11-1- <i>Layout</i> da Placa de Aquisição de Dados.....</b>                            | 131 |

| <b>Figura 11-2 <i>Layout</i> da Placa de Aquisição do <i>Drives</i> de Comando .....</b>         | 131 |

| <b>Figura 11-3 <i>Layout</i> da Placa Mão para os <i>Driver</i> de Comando e interfaces.....</b> | 132 |

## SIMBOLOGIA

### 1. Acrônimos e Abreviaturas

| <b>Símbolo</b> | <b>Significado</b>                                          |

|----------------|-------------------------------------------------------------|

| CA             | Corrente Alterna                                            |

| CC             | Corrente Contínua                                           |

| CI             | Círculo Integrado                                           |

| IGBT           | <i>Insulated Gate Bipolar Transistor,</i>                   |

| PWM            | <i>Pulse With Modulation</i>                                |

| DSP            | <i>Digital Signal Processor</i>                             |

| ADC            | <i>Analogic to Digital Converter</i>                        |

| FTMA           | Função de Transferência de Malha Aberta                     |

| CMOS           | <i>Complementary Metal Oxide Semiconductor,</i>             |

| ROM            | <i>Read Only Memory</i>                                     |

| DARAM          | <i>Dual Access Random Access Memory</i>                     |

| SARAM          | <i>Single Access Random Access Memory</i>                   |

| THD            | <i>Total Harmonic Distortion, Distorção Harmônica Total</i> |

| EVA            | <i>Event ManagerA</i>                                       |

| QEP            | <i>Quadrature Encoder Pulse</i>                             |

### 2. Símbolos de Unidades de Grandezas Físicas

| <b>Símbolo</b> | <b>Significado</b> |

|----------------|--------------------|

| $\Omega$       | Ohm                |

| A              | Ampére             |

| V              | Volt               |

| F              | Faraday            |

| H              | Henry              |

| Hz             | Hertz              |

|     |                     |

|-----|---------------------|

| W   | Watt                |

| VA  | Volt-Ampére         |

| VAR | Volt-Ampére Reativo |

| °   | Grau trigonométrico |

### 3. Símbolos Usados em Expressões Matemáticas

| <b>Símbolo</b>   | <b>Significado</b>                         | <b>Unidade</b> |

|------------------|--------------------------------------------|----------------|

| $V_o$            | Tensão de Saída do Conversor               | V              |

| $R_o$            | Resistência de Carga                       | $\Omega$       |

| $C_o$            | Capacitância de Carga                      | F              |

| $V_{in}$         | Tensão de Entrada do Conversor             | V              |

| $P_{in}$         | Potência de Entrada do Conversor           | W              |

| $I_{in}$         | Corrente de Entrada do Conversor           | A              |

| $V_{Lin}$        | Tensão no Indutor de Entrada               | V              |

| $\Delta I_{Lin}$ | Variação de Corrente no Indutor de Entrada | A              |

| $L_{in}$         | Indutor de Entrada                         | H              |

| $\Delta V_o$     | Variação de Corrente na Saída do Conversor | V              |

| $\Delta t$       | Intervalo de Tempo                         | s              |

| $f_s$            | Freqüência de Chaveamento                  | Hz             |

| $T_s$            | Período de Chaveamento                     | s              |

| $ma$             | Índice de Modulação                        |                |

| $V_{pab}$        | Tensão de Pico entre os Pontos a e b       | V              |

| $V_{pin}$        | Tensão de Pico de Rede Elétrica            | V              |

| $D$              | Razão Cíclica                              |                |

| $\eta$           | Rendimento do Conversor                    |                |

| $I_{Tmi}$        | Corrente no Transistor Média Instantânea   | A              |

| $I_{Tmed}$       | Corrente no Transistor Média               | A              |

| $I_{Tefi}$       | Corrente no Transistor Eficaz Instantânea  | A              |

| $I_{Tef}$        | Corrente no Transistor Eficaz              | A              |

|                  |                                            |                        |

|------------------|--------------------------------------------|------------------------|

| $I_{Dmi}$        | Corrente no Diodo Média Instantânea        | A                      |

| $I_{Dmed}$       | Corrente no Diodo Média                    | A                      |

| $I_{Defi}$       | Corrente no Diodo Eficaz Instantânea       | A                      |

| $I_{Def}$        | Corrente no Diodo Eficaz                   | A                      |

| $V_{Tpico}$      | Tensão no Transistor de Pico               | V                      |

| $V_{Dpico}$      | Tensão no Diodo de Pico                    | V                      |

| $I_{Cmi}$        | Corrente no Capacitor Média Instantânea    | A                      |

| $I_{Cmed}$       | Corrente no Capacitor Média                | A                      |

| $I_{Cefi}$       | Corrente no Capacitor Eficaz Instantânea   | A                      |

| $I_{Cef}$        | Corrente no Capacitor Eficaz               | A                      |

| $A_e$            | Área da Perna Central                      | $\text{cm}^2$          |

| $A_w$            | Área da Janela                             | $\text{cm}^2$          |

| $A_e \cdot A_w$  | Produtos das Áreas                         | $\text{cm}^4$          |

| $\ell \text{ m}$ | Comprimento do Caminho Magnético           | cm                     |

| $N$              | Número de Espira                           |                        |

| $Nfp$            | Número de Fios por Voltas                  |                        |

| $\mu o$          | Permeabilidade Magnética                   |                        |

| $\rho$           | Densidade Volumétrica                      |                        |

| $J_{max}$        | Máxima densidade de Corrente               | $\text{A}/\text{cm}^2$ |

| $B_{max}$        | Máxima densidade de Fluxo                  | $\text{A}/\text{cm}^2$ |

| $P_{cu}$         | Perda no Cobre                             | W                      |

| $P_{mag}$        | Perda no Núcleo                            | W                      |

| $P_{tot}$        | Perda Total                                | W                      |

| $V_{CEN}$        | Tensão de Saturação Coletor Emissor        | V                      |

| $V_{CEO}$        | Tensão Limiar de Saturação Coletor Emissor | V                      |

| $I_{CN}$         | Corrente Nominal de Coletor                | A                      |

| $I_{CM}$         | Valor Máximo da Corrente na Carga.         | A                      |

| $tr$             | Tempo de Subida na Entrada em Condução     | s                      |

| $trr$            | Tempo da Corrente de Recuperação Reversa   | s                      |

| $fs$             | Freqüência de Chaveamento                  | Hz                     |

| $Qrr$            | Carga Armazenada no Diodo em Condução      | C                      |

|             |                                       |       |

|-------------|---------------------------------------|-------|

| $P_{cond}$  | Perda por Condução                    | W     |

| $P_{on}$    | Perda na Entrada em Condução          | W     |

| $P_{off}$   | Perda no Desligamento                 | W     |

| $DP_{Max}$  | Penetração Máxima de Corrente         | cm    |

| $P_{chave}$ | Perdas na Chave                       | W     |

| $P_{diodo}$ | Perdas no Diodo                       | W     |

| $T_{ck}$    | Período do <i>Clock</i>               | s     |

| $f_{ck}$    | Freqüência de <i>Clock</i>            | Hz    |

| $V_H$       | Tensão de Referência Alta do ADC      | V     |

| $T_{off}$   | Tempo do PWM desligado                | s     |

| $T_{PWM}$   | Período do PWM                        | s     |

| $K_{PWM}$   | Ganho do PWM                          |       |

| $K_{AD}$    | Ganho do ADC                          |       |

| $K_{si}$    | Ganho do Sensor de Corrente           |       |

| $K_{sv}$    | Ganho do Sensor de Tensão             |       |

| $K_{Hi}$    | Ganho do Controlador de Corrente      |       |

| $K_{Hv}$    | Ganho do Controlador de Tensão        |       |

| $K_M$       | Ganho do Multiplicador                |       |

| $V_{DIG}$   | Tensão de Entrada do ADC Digitalizada |       |

| $V_{AN}$    | Tensão de Entrada do ADC              | V     |

| $V_{HI}$    | Tensão de Alimentação Alta do ADC     | V     |

| $V_{LO}$    | Tensão de Alimentação Baixa do ADC    | V     |

| $I_p$       | Corrente de Fundo de Escala do Sensor | A     |

| $I_{pn}$    | Range da Corrente a Ser Medida        |       |

| $T_a$       | Período de Amostragem                 | s     |

| $\nu$       | Freqüência no domínio de w            | rad/s |

| $\omega$    | Freqüência no domínio de s            | rad/s |

| $f_c$       | Freqüência de cruzamento              | Hz    |

#### 4. Subíndices

| <u>Símbolo</u> | <u>Significado</u>       |

|----------------|--------------------------|

| min            | Valor Mínimo             |

| max            | Valor Máximo             |

| med            | Valor Médio              |

| mi             | Valor Médio Instantâneo  |

| ef             | Valor Eficaz             |

| efi            | Valor Eficaz Instantâneo |

| i              | Malha de Corrente        |

| v              | Malha de Tensão          |

## 5. Notações Matemáticas

| <u>Símbolo</u> | <u>Significado</u>     |

|----------------|------------------------|

| $\bar{A}$      | Grandeza Parametrizada |

## INTRODUÇÃO GERAL

É crescente o número de equipamentos eletro-eletrônicos e eletromecânicos que utilizam fontes de alimentação especiais, como retificadores controlados, inversores, fontes chaveadas e outras, e isto vem causando perturbações relevantes no sistema de energia elétrica, contribuindo para o desgaste do sistema, como por exemplo, através do aquecimento dos condutores pela presença de harmônicas, além do desperdício de energia.

Os principais distúrbios causados nas instalações elétricas são basicamente três:

Fator de potência baixo;

Elevada distorção harmônica;

Interferências eletromagnéticas provocada pelas harmônicas.

As companhias distribuidoras de energia do Brasil ainda não levam em conta este tipo de desperdício no momento da cobrança da energia fornecida, porém novas normas e recomendações internacionais, possivelmente, levarão as companhias a mudanças em seus métodos de avaliação e cobrança da energia que deverá considerar, entre outros, o fator de potência, a taxa de distorção harmônica total (THD) e a emissão de ruídos (EMI).

Com este novo posicionamento das companhias de energia será necessária a minimização de tais problemas, através de projetos de equipamentos que façam o controle destes efeitos, procurando a sua conseqüente redução. Muitos estudos têm sido desenvolvidos nestas áreas na busca de soluções preventivas onde o próprio equipamento já utiliza alguma técnica de redução de conteúdo harmônico ou de correção de fator de potência.

Quando se faz necessária a correção do fator de potência, da taxa de distorção de harmônica total (THD) e a da emissão de ruídos (EMI) em equipamentos que já se encontram em funcionamento e que não possuem técnicas preventivas para redução destes problemas, deve-se recorrer ao uso de técnicas corretivas. Uma solução possível seria o emprego de filtros passivos, porém, apesar destes filtros serem robustos, apresentam um volume e peso exagerados.

Outra solução que tem sido adotada com bastante êxito é a utilização de filtros ativos monofásicos de pequena e média potência paralelos aos equipamentos com problemas de distorções e baixo fator de potência.

Esta alternativa se torna ainda mais atraente quando a estrutura do filtro possui um controle feito através de processamento digital, pois este fator faz com que ocorra redução de componentes eletrônicos nas placas de comando dos conversores, e tornam estes conversores mais flexíveis, pois seu controle pode ser mudado apenas mudando o programa do controlador digital, além de diminuir o tempo de montagem do produto final, assim minimizando o número de componentes eletrônicos susceptíveis a ruídos.

Outra aplicação, do trabalho é a de melhorar o fator de potência em acionamentos de motores que utilizam inversores de freqüência, onde um retificador reversível controlado com alto fator de potência pode contribuir para a eliminação das harmônicas indesejadas. Além disso, estes retificadores possuem, nesta configuração, o efeito regenerativo de energia, o que contribui para a consequente eficiência energética dos acionamentos, pois eliminam o uso das resistências de frenagem utilizadas para dissipar a energia elétrica produzida na frenagem dos motores, ao invés de devolvê-la a rede como se faz nos retificadores reversíveis em corrente.

Partindo deste ponto, este trabalho faz um estudo do projeto de um conversor monofásico reversível em corrente, com fator de potência elevado, utilizando métodos de controle digitais, baseados no método de controle através dos Valores Médios.

Inicialmente é feito, através do Capítulo I, o estudo qualitativo do conversor, onde é apresentada a estrutura do conversor, o princípio geral de funcionamento nos diversos quadrantes de operação.

Logo em seguida, no Capítulo II, é feita a análise quantitativa do conversor através da definição das principais equações, que serão utilizadas na implementação do controle e na especificação dos componentes.

Então, no Capítulo III, são utilizadas as equações estabelecidas no capítulo anterior para projetar adequadamente o circuito de potência para definir os parâmetros de projeto que caracterizam o conversor.

No Capítulo IV, é feito um estudo do projeto do compensador digital para o conversor. Neste estudo será utilizado o método de *Controle por Valores Médios*, porém a ênfase aqui será dada à aplicação do uso dos compensadores usando a técnica digital.

No Capítulo V são apresentados os resultados obtidos através de simulações utilizando o MATLAB® a fim de averiguar a validade das leis de controle projetadas no capítulo anterior.

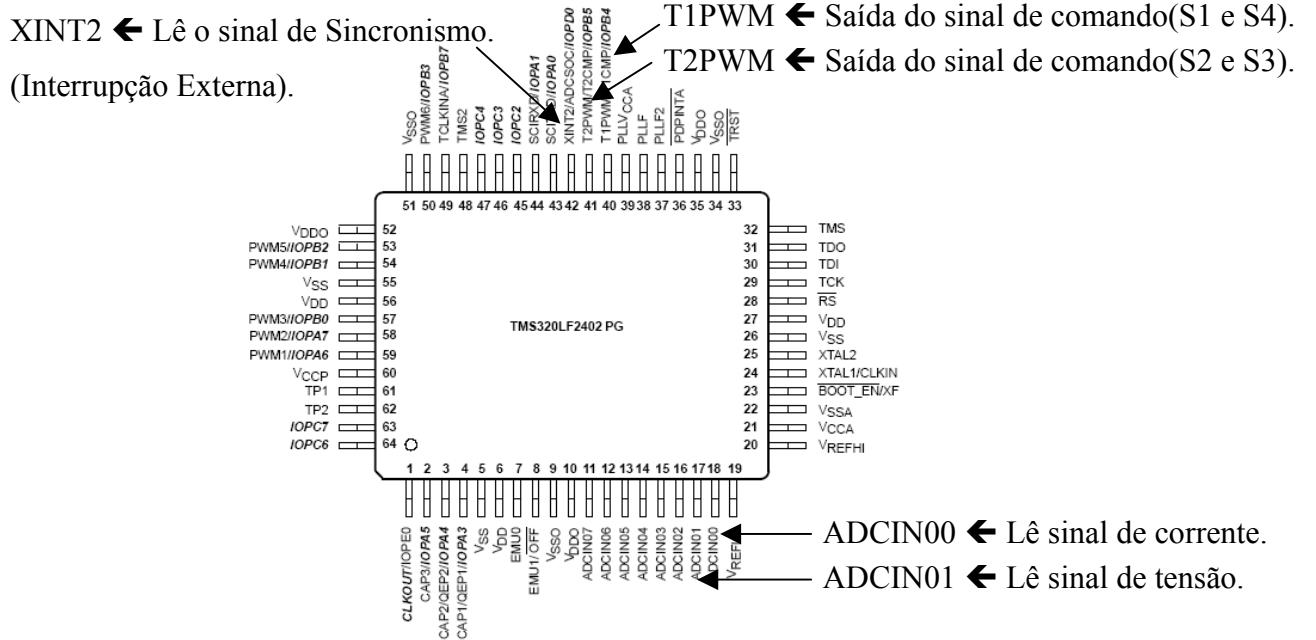

No Capítulo VI é feito um estudo do processador digital de sinais, DSP TMS320LF2402 que será utilizado para implementação do projeto, procurando detalhar a questão da representação numérica de uma grandeza tanto no formato de ponto fixo, quanto no formato de ponto flutuante, e também da utilização de periféricos.

Por fim, no Capítulo VII, será apresentada a estrutura montada para os testes práticos das leis de controles e o resultados obtidos.

Após este último capítulo são apresentadas as conclusões gerais e anexos.

# CAPÍTULO 1

## 1 ESTUDO QUALITATIVO DO CONVERSOR

Neste capítulo é feito um estudo do conversor de corrente reversível monofásico. Este conversor é utilizado comumente em circuitos de correção ativa de fator de potência que necessitam de regeneração de energia proveniente da frenagem de motores, regulação da tensão CC do barramento. Também são usados em outras aplicações, como filtros ativos, condicionadores de sinal, recicladores de energia, co-geração, dentre outras.

Uma característica deste retificador é o comportamento de uma fonte de corrente no estágio de entrada, ao invés da fonte de tensão presente na maioria dos retificadores.

### 1.1 A Estrutura do Conversor

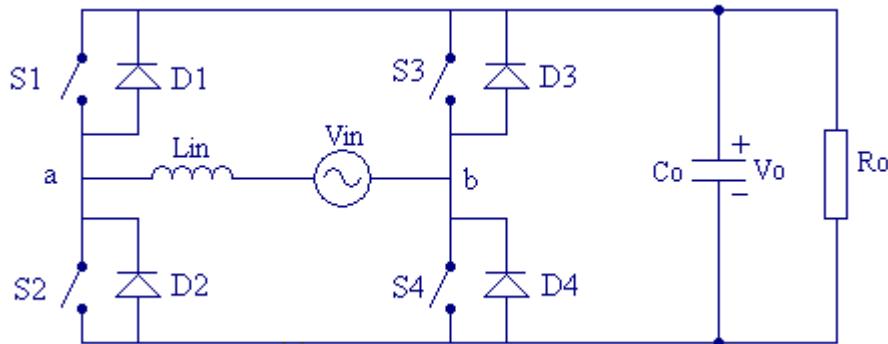

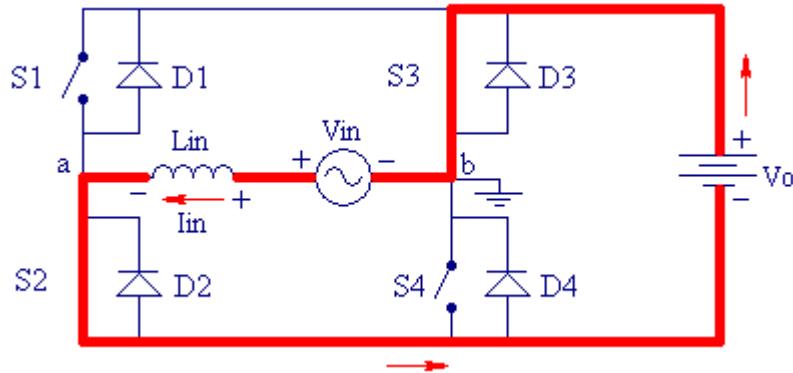

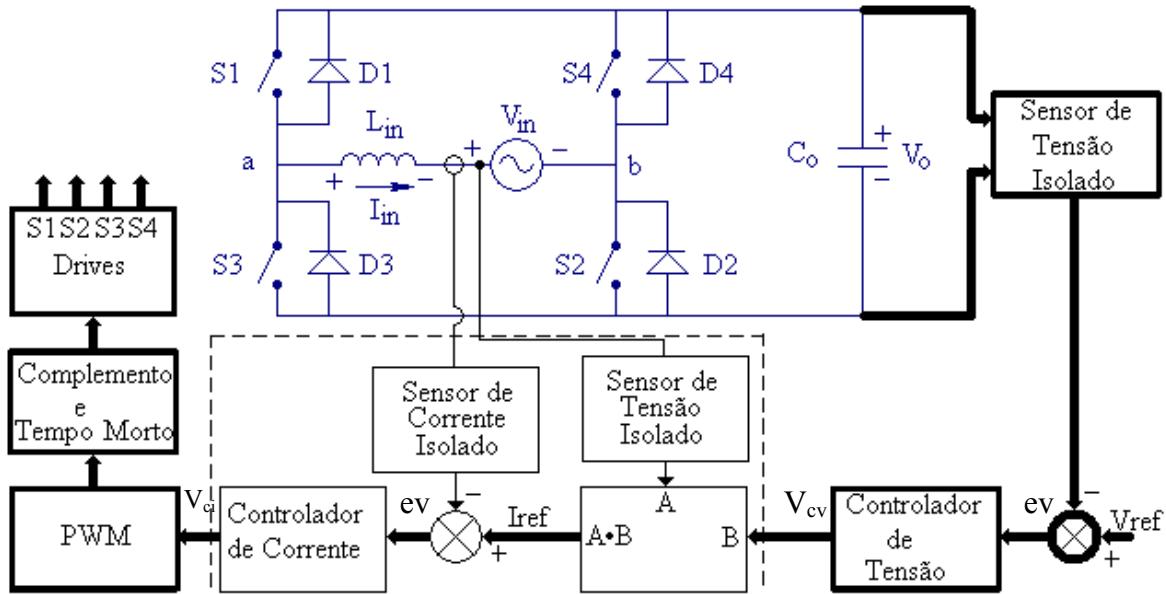

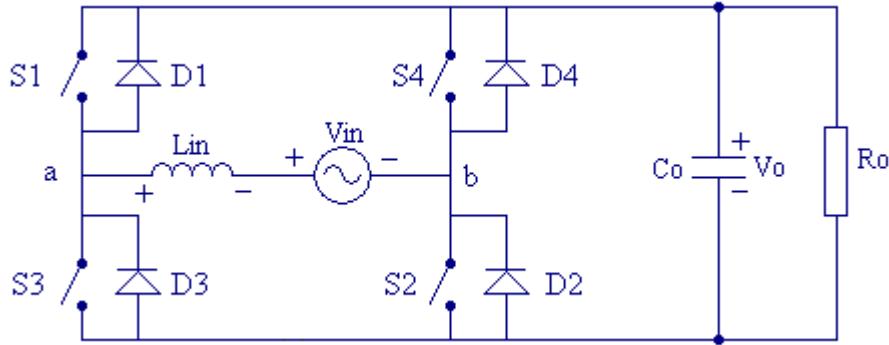

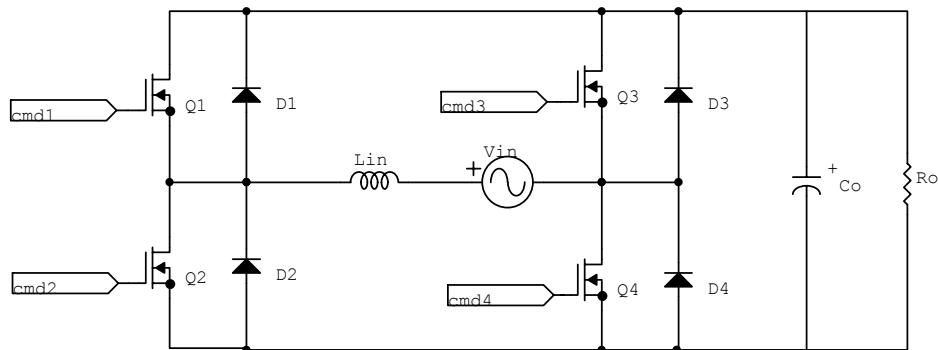

A estrutura do conversor a ser estudada é a mostrada na figura 1-1, a qual é conectada a rede através de um indutor  $L_{in}$ . O lado CC do conversor é conectado a um capacitor de filtragem  $C_o$ .

Figura 1-1 Conversor reversível de corrente monofásico.

Este circuito pode funcionar também com inversor. Isto ocorre quando a estrutura trabalha com um fluxo de potência da fonte  $V_o$  (CC) para a fonte  $V_{in}$  (CA). O circuito funciona dessa maneira nos períodos de frenagem do motor, possibilitando desse modo que a energia seja devolvida para a rede de alimentação.

De uma maneira geral, o enfoque deste projeto será estabelecido para o funcionamento com retificador, onde o fluxo de potência ocorre da fonte  $V_{in}$  (CA) para a fonte  $V_o$  (CC), que caracteriza o barramento de corrente contínua.

É importante salientar que a fonte  $V_o$  é formada pela configuração paralela capacitor-resistor, a qual origina uma fonte CC, como pode ser visto através da figura 1-1.

## 1.2 Princípios de Funcionamento

Nesta seção são analisadas as características de funcionamento do conversor, bem como seus principais quadrantes de operação.

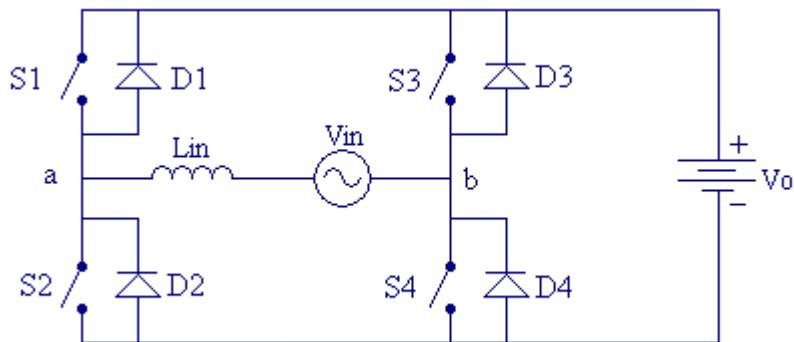

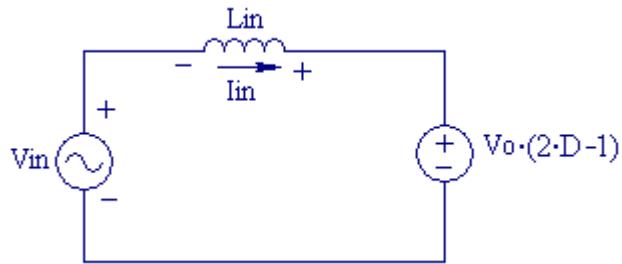

Devido a simetria deste conversor será analisado apenas meio período da rede, e como a tensão na saída pode ser considerada constante, o capacitor da saída e a carga podem ser substituídos por uma fonte ideal de tensão, para simplificar a análise, como mostrado na figura 1-2.

**Figura 1-2 Conversor reversível de corrente monofásico.**

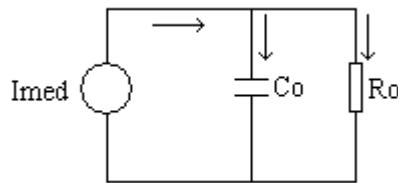

Além disso, deve ser reforçado que fonte de tensão associada com uma indutância em série comporta-se com uma fonte de corrente, com mostra a figura 1-3.

**Figura 1-3 Estrutura representativa de um fonte de corrente.**

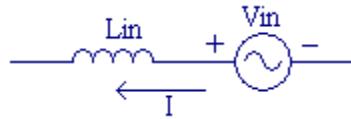

É, no entanto, necessário que sejam definidas as etapas de acordo com o sentido da corrente elétrica e polaridade da fonte de alimentação. Deste modo, será adotado um padrão para cada etapa de funcionamento do circuito.

A figura 1-4 mostra apenas a fonte de alimentação senoidal o indutor que estão presentes na entrada do circuito. Verifica-se então, a polaridade da fonte de tensão e o

sentido da corrente. Isto caracteriza o quadrante de operação do circuito, na qual a polaridade da fonte de tensão, como mostrado na figura, é padronizada como estando atuando no semiciclo positivo. Desta maneira, se a corrente estiver “saindo” pelo positivo da fonte, será uma corrente positiva; se a corrente estiver “entrando” pelo positivo da fonte, será uma corrente negativa.

**Figura 1-4 Referência adotada para tensão e corrente positivas.**

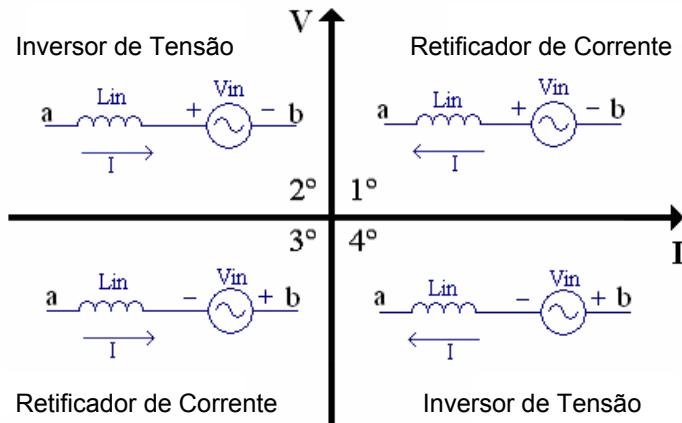

Através desta convenção, é possível verificar que as referências para tensão e corrente positiva são as que estão mostradas na figura 1-4. Como existem diferentes configurações de tensão e corrente, um plano cartesiano será adotado como padrão, onde o eixo de ordenada representa a tensão e o eixo de abscissa representa a corrente. A figura 1-5 mostra o plano cartesiano, com as respectivas polaridades para tensão e corrente.

**Figura 1-5 Representação dos quadrantes de operação.**

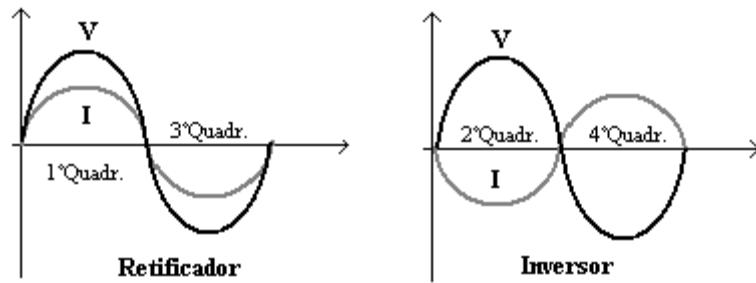

A partir da figura 1-5, podem ser verificadas as respectivas referências para cada quadrante, onde o circuito pode funcionar como retificador ou inversor:

- 1º quadrante: corrente positiva e tensão positiva – retificador;

- 2º quadrante: corrente negativa e tensão positiva – inversor;

- 3º quadrante: corrente negativa e tensão negativa – retificador;

- 4º quadrante: corrente positiva e tensão negativa – inversor.

Para reforçar esta análise, pode-se verificar o comportamento dos formatos de onda da tensão e corrente nas diferentes operações do circuito, de acordo com a figura 1-5. Aqui já é estabelecida uma característica de fator de potência unitário, onde a forma de onda da corrente é praticamente senoidal. Quando o circuito opera como inversor, figura 1-6, ocorre um desfasamento de  $180^\circ$  entre tensão e corrente. A título de ilustração, os valores de tensão são representados como tendo um escala maior do que os valores de corrente.

**Figura 1-6 Comportamento das formas de onda para Retificador e Inversor.**

Para verificar se o circuito se comporta com retificador ou inversor, a abordagem é feita em relação ao fluxo de potência, onde a potência é definida com a relação *tensão x corrente*. Se esta relação for positiva, caracteriza um fluxo de potência positivo, resultando assim uma operação com retificador, onde a fonte de tensão fornece energia para o barramento. Por outro lado, se a relação *tensão x corrente* for negativa, o fluxo de potência é negativo e o circuito opera como inversor, fazendo com que a fonte de tensão seja receptora de energia proveniente do barramento.

Após estas definições, vale salientar também que em cada quadrante existem duas etapas de operação, totalizando oito configurações diferentes. Para melhor compreensão serão mostradas aqui as quatro etapas em que o conversor atua como retificador.

## 1.3 Etapas de Funcionamento como Retificador

Nesta seção são descritas as etapas de funcionamento e formas de ondas básicas do conversor de corrente reversível monofásico. A cada período de chaveamento a corrente no indutor pode ser positiva, negativa ou ambas. Serão analisadas as duas primeiras possibilidades.

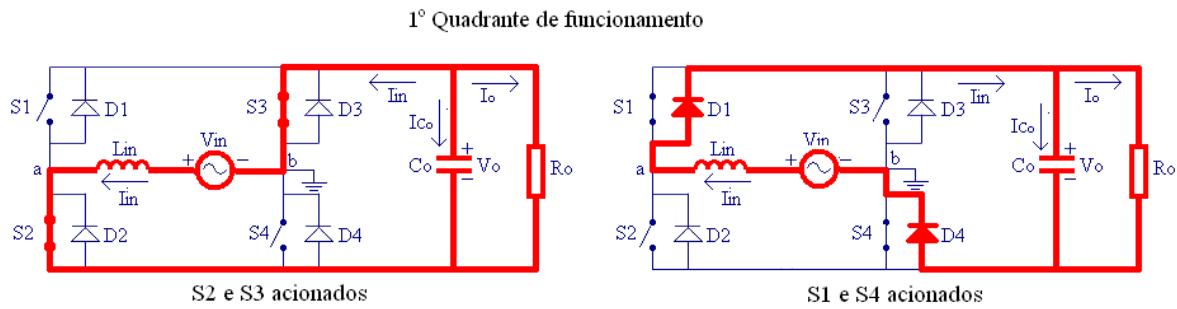

### 1.3.1 Funcionamento no 1º Quadrante

#### 1ª Etapa( $T_0, T_1$ )

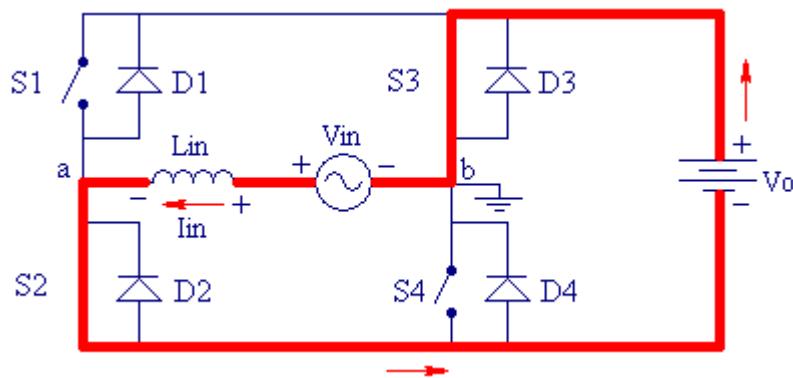

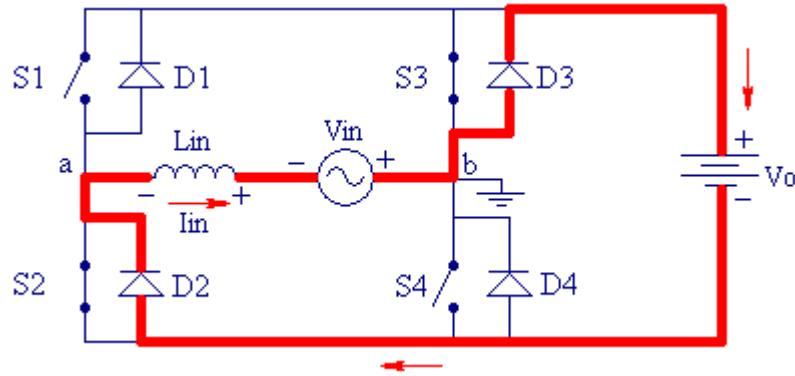

Nesta etapa de operação, a região do circuito por onde passa corrente é a mostrada na figura 1-7. A corrente circula da fonte  $V_o$  para a fonte de alimentação  $V_{in}$ , através das chaves S2 e S3.

Figura 1-7 1ª etapa de operação para 1º quadrante.

A partir das convenções adotadas, a fonte alternada está em seu semiciclo positivo, porém a corrente presente também é positiva, caracterizando ainda um fluxo de potência positivo. Portanto, o circuito opera no 1º quadrante, e também está fazendo a função de retificador.

O comando que habilita as chaves S2 e S3 a conduzirem, é realizado através de modulação PWM (*Pulse Width Modulation* – Modulação por Largura de Pulso), efetuada através da estrutura de comando e controle do sistema, sendo abordada mais adiante.

Considerando as chaves ideais, a tensão sobre o indutor pode ser calculada pela Eq.1-1.

$$V_{Lin} - V_{in} - V_o = 0 \quad \text{Eq. 1-1}$$

ou ainda

$$V_{Lin} = +V_o + V_{in} \quad \text{Eq.1-2}$$

Neste intervalo o indutor se carrega, aumentando a corrente que circula pelo circuito.

### 2<sup>a</sup> Etapa (T<sub>1</sub>,T<sub>2</sub>)

Nesta etapa, o comando habilita as chaves S1 e S4 a conduzirem, fazendo com que S2 e S3 deixem de conduzir. Porém, S1 e S4 não podem conduzir devido ao sentido da corrente, possibilitando que a condução ocorra através dos diodos D1 e D4 durante este intervalo de tempo. O circuito por onde passa corrente nesta situação é mostrado na figura 1-8.

Figura 1-8 2<sup>a</sup> etapa de operação para 1º quadrante.

Novamente a região de operação se encontra no 1º quadrante. Agora, a fonte  $V_o$  atua como um receptor de energia, descarregando parte da energia do indutor e diminuindo a corrente no circuito.

Considerando a queda de tensão nos diodos como praticamente nula, a tensão sobre o indutor é dada pela Eq.1-3.

$$V_{Lin} - V_{in} + V_o = 0 \quad \text{Eq. 1-3}$$

Isolando  $V_{Lin}$  na equação anterior vem a Eq.1-4

$$V_{Lin} = -V_o + V_{in} \quad \text{Eq. 1-4}$$

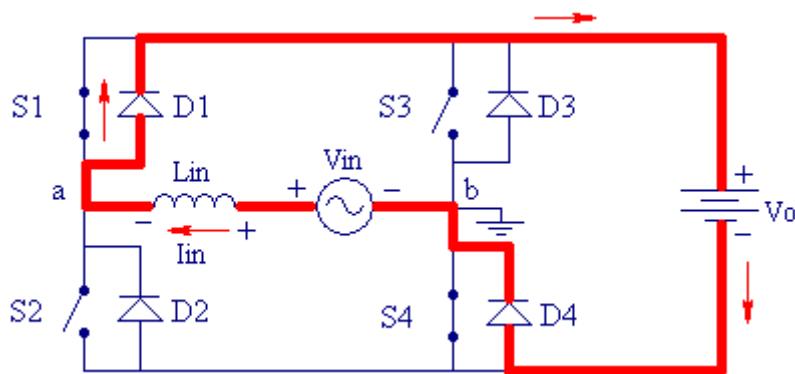

Na figura 1-9 é possível observar que a tensão sobre o indutor varia de acordo com os valores estabelecidos nas Eq. 1-1 e Eq. 1-4. No momento em que a tensão é negativa, a corrente decresce. Quando a tensão é positiva, a corrente é incrementada. A variação de corrente no indutor é representada pela Eq.1-5.

$$\Delta I_{Lin} = \frac{V_{Lin}}{L_{in}} \cdot \Delta t \quad \text{Eq. 1-5}$$

A partir desta equação verifica-se que a corrente sobre o indutor tem comportamento linear, seguindo a equação de uma reta. Assim, no momento em que a tensão sobre o indutor se torna positiva, a corrente tende a crescer linearmente até o seu valor máximo.

O formato de onda de tensão no indutor não precisa ser necessariamente quadrado. O que determina o tempo de condução é a razão cíclica D, a qual será estabelecida em projeto e tem sua aplicação no sistema de controle através da modulação PWM.

Nas chaves S2 e S3 (figura 1-9) a corrente que circula é a mesma corrente do indutor, na 1<sup>a</sup> etapa de operação. A queda de tensão nas chaves é considerada nula. Já na 2<sup>a</sup> etapa, não passa corrente por estas chaves e, como elas estão bloqueadas, a tensão sobre cada uma é a tensão de saída  $V_o$ .

A corrente que passa nos diodos D1 e D4 na 2<sup>a</sup> etapa é a mesma que passa pelo indutor, porém a corrente que passa através dos diodos D2 e D3 é nula. Quando polarizados reversamente, a tensão sobre eles é  $V_o$ . Nas demais chaves a análise é semelhante, cabendo ao leitor verificar o comportamento de cada um dentro da sua respectiva etapa de operação.

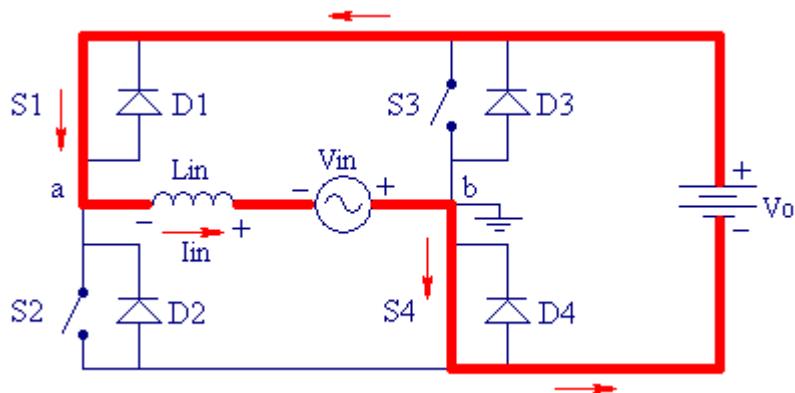

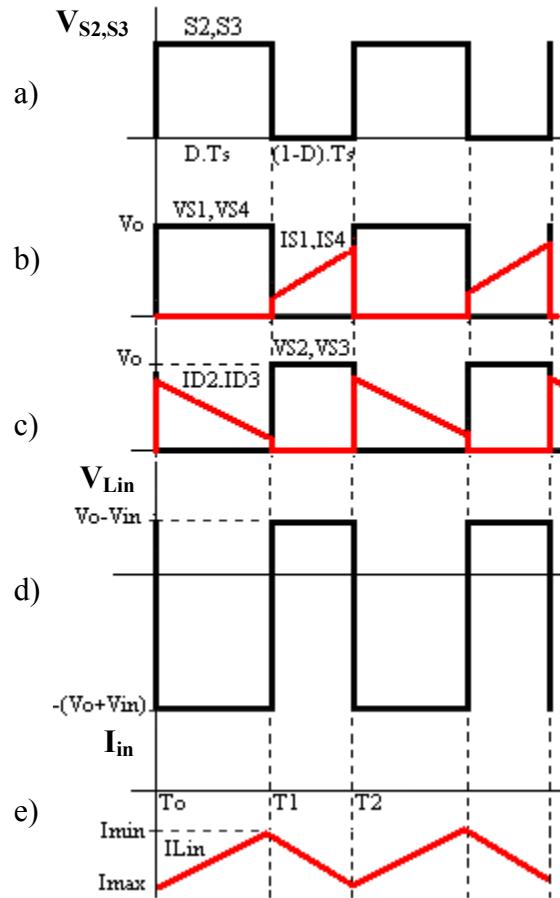

**Figura 1-9 Formas de onda para 1º quadrante. (a) Pulso de comando nas chaves S2 e S3. (b) Tensão em S1 e S4 e Corrente em D1 e D4. (c) Tensão em VS2 e VS3 e corrente em S2 e S3. (d) Tensão sobre o indutor. (e) Corrente no Indutor.**

### 1.3.2 Funcionamento no 3º Quadrante

#### 1ª Etapa( $T_0, T_1$ )

Nesta etapa, o comando habilita as chaves S2 e S3 a conduzirem, fazendo com que S1 e S4 deixem de conduzir. Porém, S2 e S3 não podem conduzir devido ao sentido da corrente, possibilitando que a condução ocorra através dos diodos D2 e D3 durante este intervalo de tempo. O circuito por onde passa corrente nesta situação é mostrado na figura 1-10.

Figura 1-10 1<sup>a</sup> etapa de operação para 3º quadrante.

Novamente a região de operação se encontra no 3º quadrante. Agora, a fonte  $V_o$  atua como um receptor de energia, descarregando parte da energia do indutor e diminuindo a corrente no circuito.

Considerando a queda de tensão nos diodos como praticamente nula, a tensão sobre o indutor é dada pela Eq.1-6.

$$V_{Lin} + V_{in} - V_o = 0 \quad \text{Eq. 1-6}$$

Da mesma forma isolando  $V_{Lin}$  na equação anterior vem a Eq.1-7

$$V_{Lin} = +V_o - V_{in} \quad \text{Eq. 1-7}$$

## 2<sup>a</sup> Etapa

Nesta etapa de operação, a região do circuito por onde passa corrente é a mostrada na figura 1-11. A corrente circula da fonte de alimentação  $V_{in}$  para a fonte  $V_o$ , que representa o barramento CC, através das chaves S1 e S4.

Figura 1-11 2<sup>a</sup> etapa de operação para 3º quadrante.

A partir das convenções adotadas, a fonte alternada está em seu semiciclo negativo e a corrente presente também é negativa, caracterizando um fluxo de potência positivo. Portanto, o circuito opera no 3º quadrante, fazendo a função de retificador.

Considerando as chaves ideais, a tensão sobre o indutor pode ser facilmente calculada, através da lei das malhas, dada pela Eq.1-8. A polaridade da tensão sobre o indutor foi definida arbitrariamente, sendo assim escolhida para estabelecer uma referência.

$$V_{Lin} + V_{in} + V_o = 0 \quad \text{Eq. 1-8}$$

O que resulta por fim na Eq.1-9

$$V_{Lin} = -(V_o + V_{in}) \quad \text{Eq. 1-9}$$

Neste intervalo o indutor se carrega, aumentando a corrente que circula pelo circuito.

Como no funcionamento no 1º quadrante, a figura 1-12 mostra a tensão sobre o indutor, que também varia de acordo com os valores estabelecidos nas Eq. 1-1 e Eq. 1-2. No momento em que a tensão é negativa, a corrente decresce. Quando a tensão é positiva, a corrente é incrementada. A variação de corrente no indutor é representada pela Eq.1-3.

O formato de onda de tensão no indutor não precisa ser necessariamente quadrado. O que determina o tempo de condução é a razão cíclica D, a qual será estabelecida em projeto e tem sua aplicação no sistema de controle através da modulação PWM.

Na 1ª etapa, nas chaves S1 e S4 (figura 1-1211) não passa corrente por estas chaves e, como elas estão bloqueadas, a tensão sobre cada uma é a tensão de saída  $V_o$ . Já a corrente que circula é a mesma corrente do indutor, na 2ª etapa de operação. A queda de tensão nas chaves é considerada nula.

Através dos diodos D1 e D4 não passa corrente em nenhum momento. Quando polarizados reversamente, a tensão sobre eles é  $V_o$ . Nos diodo D2 e D3 a corrente é a mesma que passa pelo indutor durante a 1ª etapa de funcionamento, porém na segunda corrente é nula.

**Figura 1-12** Formas de onda para 3º quadrante. (a) Pulso de comando nas chaves  $S_2$  e  $S_3$ . (b) Tensão em  $S_1$  e  $S_4$  e Corrente em  $S_1$  e  $S_4$ . (c) Tensão em  $VS_2$  e  $VS_3$  e corrente em  $D_2$  e  $D_3$ . (d) Tensão sobre o indutor. (e) Corrente no Indutor.

## 1.4 Conclusões

Foi possível contemplar neste capítulo a estrutura do conversor a ser estudado, bem como seu o seu funcionamento. Foi possível também observar que uma característica deste retificador é a presença de uma fonte de corrente no estágio de entrada, ao invés da fonte de tensão presente na maioria dos retificadores.

Na analise do funcionamento ficou relevante que para o funcionamento do conversor analisado como retificador, é necessário que o fluxo de potência ocorre da fonte  $V_{in}$  (CA) para a fonte  $V_o$  (CC), que caracteriza o barramento de corrente contínua.

Por fim foram analisadas as características de funcionamento do conversor, bem como seus principais quadrantes de operação. Além das descrições das etapas de funcionamento e formas de ondas básicas do retificador de corrente reversível monofásico.

# CAPÍTULO 2

## 2 ANALISE QUANTITATIVA DO CONVERSOR

Neste capítulo será feito a análise quantitativa do conversor através da definição das principais equações que serão utilizadas para a implementação do controle e na especificação dos componentes. As especificações dos componentes, realizadas no próximo capítulo, serão feitas através dos cálculos dos esforços apresentados neste item.

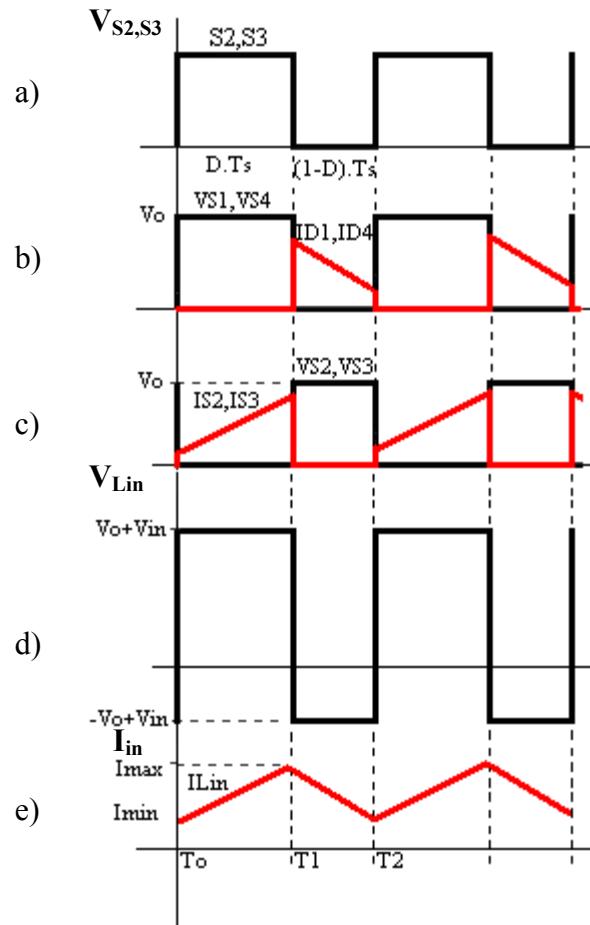

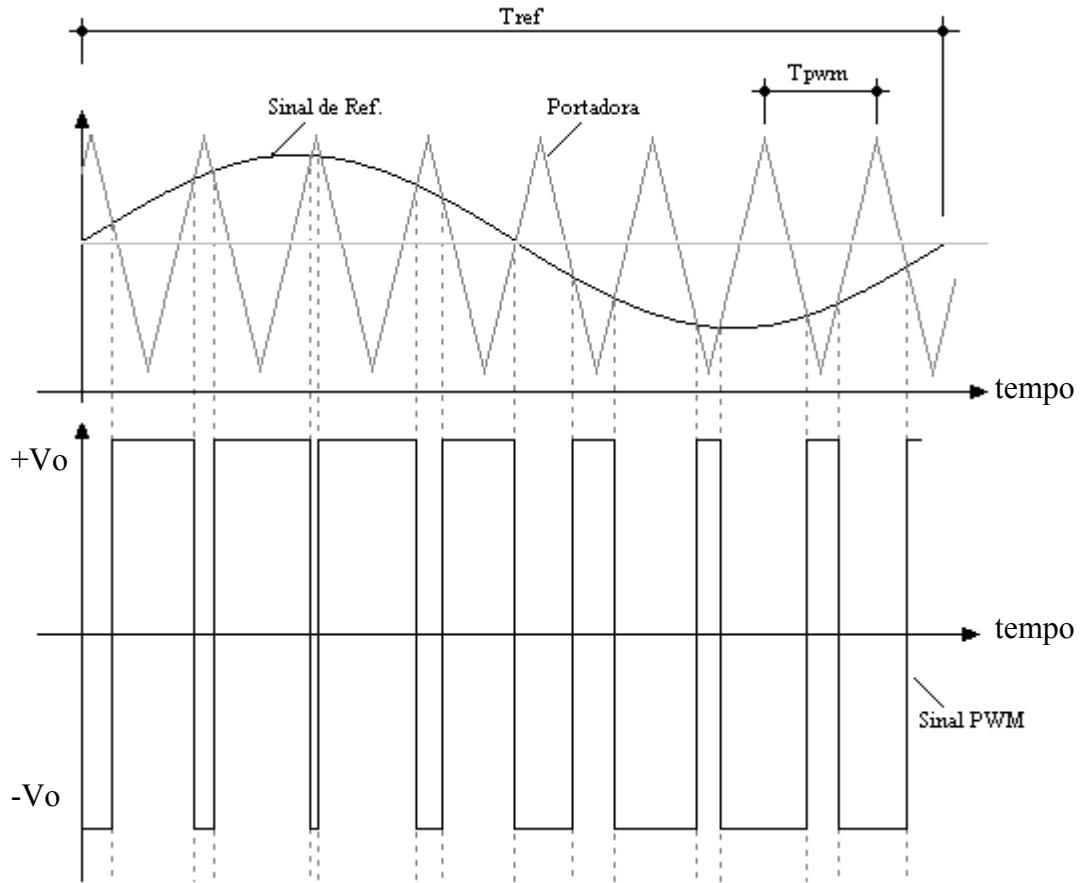

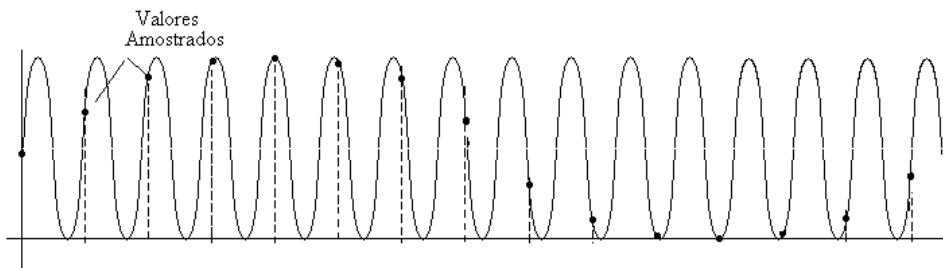

### 2.1 Análise Quantitativa

Para iniciar a análise quantitativa é necessário que seja apresentada inicialmente a técnica de comando utilizada para o chaveamento do retificador. Esta técnica é a mais empregada nestes tipos de estrutura e é denominada de Modulação por Largura de Pulso ou PWM (*Pulse Width Modulation*). Esta técnica baseia-se na comparação de dois sinais denominados sinal modulador e sinal portador, onde o sinal portador possui uma freqüência muito maior que o sinal modulador e geralmente possui uma forma triangular; já o sinal modulador possui uma freqüência baixa, a qual é um espelho da fonte de alimentação. De acordo com os princípios da modulação PWM, as chaves são habilitadas sempre que o valor da onda portadora for maior que o sinal de referência senoidal, como mostra a figura 2-1.

Figura 2-1 Processo de geração de sinal PWM.

O sinal portador possui uma freqüência dada pela Eq.2-1.

$$f_s = \frac{1}{T_s} \quad \text{Eq. 2-1}$$

Onde,  $T_s$  é o período de chaveamento.

O índice de modulação deste sinal PWM representa a relação entre a amplitude do sinal modulador e a amplitude do sinal portador, dado pela Eq.2-2.

$$ma = \frac{V_{p_{moduladora}}}{V_{p_{portadora}}} = \frac{V_{Pab}}{V_o} \quad \text{Eq. 2-2}$$

## 2.2 Definição das Principais Equações

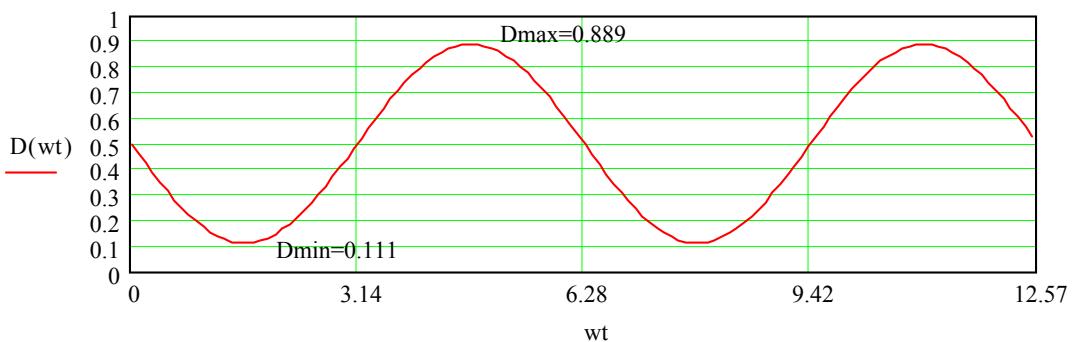

Olhando para um intervalo de tempo  $T_{PWM}$ , onde a tensão sobre o ponto  $V_{ab}$  varia entre dois níveis  $+V_o$  e  $-V_o$ . Sendo  $D$  a razão cíclica, a tensão média aplicada à carga no respectivo período PWM ( $T_{PWM}$ ), pode ser calculada através da Eq.2-3.

$$V_{ab_{med}} = \frac{1}{T_s} \left[ \int_0^{DT_s} (-V_o) \cdot dt + \int_{DT_s}^{T_s} V_o \cdot dt \right] \quad \text{Eq. 2-3}$$

Trabalhando esta equação tem se a Eq.2-4.

$$V_{ab_{med}} = V_o \cdot (1 - 2D) \quad \text{Eq. 2-4}$$

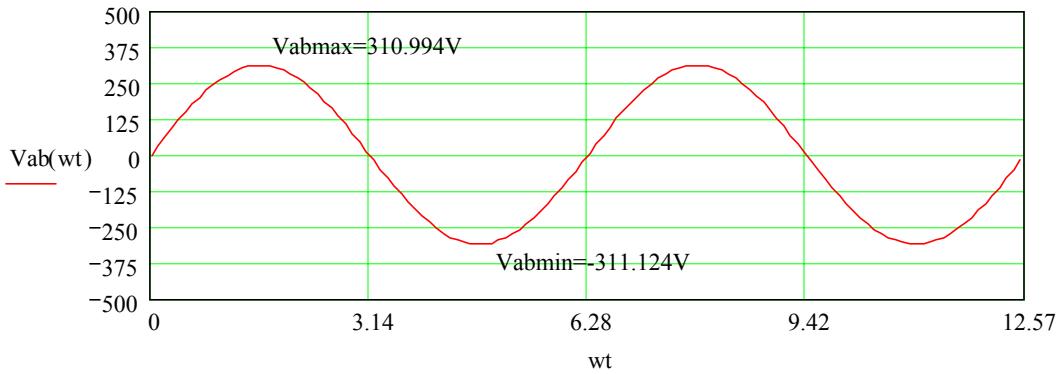

No entanto, para um período da rede  $T_{ref}$ , a tensão no ponto  $V_{ab}$  varia senoidalmente. Então, desprezando a queda de tensão sobre o indutor de entrada( $L_{in}$ ) a Tensão  $V_{ab}$  para o período da rede pode calculada através da Eq.2-5.

$$V_{ab}(\omega t) = V_{in} = V_{Pin} \operatorname{sen} \omega t \quad \text{Eq. 2-5}$$

Logo  $V_{ab} = V_{Pin}$

Onde,  $V_{Pin}$  é o valor de pico da tensão de entrada e  $\omega = \frac{2\pi}{T_{ref}}$ .

A amplitude da tensão de entrada pode ser expressa em função do índice de modulação através da Eq.2-6:

$$\frac{V_{Pab}}{V_o} = ma$$

$$V_{Pab} = V_o \cdot ma \quad \text{Eq. 2-6}$$

Logo, a tensão de entrada pode ser reescrita substituindo a Eq. 2-5 na Eq. 2-4, resultando assim na Eq.2-7:

$$V_{ab}(\omega t) = V_o \cdot ma \cdot \sin \omega t \quad \text{Eq. 2-7}$$

Combinando a Eq. 2-4 com a Eq. 2-6, é possível encontrar a variação da razão cíclica.

$$V_o \cdot ma \cdot \sin \omega t = V_o \cdot (1 - 2D)$$

$$D(\omega t) = \frac{1}{2} \cdot (1 - ma \cdot \sin \omega t) \quad \text{Eq. 2-8}$$

A razão cíclica utilizada pelo comando PWM deve variar conforme a Eq. 2-8 que é mostrada graficamente através da figura 2-2.

**Figura 2-2 Variação da razão cíclica em função de  $\omega t$ .**

Assim pode ser traçada a forma de onda de  $V_{ab}$  em função da razão cíclica, que como visto anteriormente, deve ter um forma de onda senoidal. Esta forma de onda é mostrada na figura 2-3.

**Figura 2-3 Variação da Tensão entre os pontos *a* e *b* em função da razão cíclica.**

Por fim, a corrente na entrada pode ser dada pela relação entre a potência e a tensão de entrada, com mostra a Eq.2-9.

$$I_{in}(\omega t) = \sqrt{2} \cdot \frac{P_{in}}{V_{in}} \cdot \operatorname{sen} \omega t \quad \text{Eq. 2-9}$$

Onde  $P_{in}$  é a potência de entrada do conversor e que pode ser relacionada com a potência da saída através a Eq.2-10:

$$P_{in} = \frac{P_o}{\eta} \quad \text{Eq. 2-10}$$

Onde  $\eta$  é o rendimento do conversor.

A potência de entrada pode ser relacionada com a tensão e carga de saída como:

$$P_o = \frac{V_o^2}{R_o} \quad \text{Eq.2-11}$$

assim,

$$P_{in} = \frac{1}{\eta} \cdot \frac{V_o^2}{R_o} \quad \text{Eq.2-12}$$

Agora a Eq. 2-9 pode ser reescrita da maneira mostrada pela Eq.2-13:

$$I_{in}(\omega t) = \frac{\sqrt{2} \cdot P_o}{\eta \cdot V_{in}} \cdot \operatorname{sen} \omega t \quad \text{Eq. 2-13}$$

## 2.3 Esforços nos Componentes

Na determinação dos esforços nos componentes, a corrente de carga será considerada constante em cada período do PWM. Além de ser levado em conta as formas de onda nos componentes do conversor nas suas respectivas etapas de funcionamento e considerar as definições relativas a modulação PWM.

### 2.3.1 Equações para Esforços das Chaves

A corrente através dos interruptores pode ser calculada utilizando apenas um período de condução do ciclo PWM, o que resulta na Eq.2-14:

$$I_{Tmi} = \frac{1}{T_S} \int_0^{T_S} I_{in} \cdot dt \quad \text{Eq. 2-14}$$

Trabalhando esta equação tem se a Eq.2-15.

$$I_{Tmi} = I_{in} \cdot D \quad \text{Eq. 2-15}$$

Assim, substituindo  $I_{in}$  e  $D$  e efetuando as manipulações necessárias temos a Eq.2-16:

$$I_{Tmi}(\omega t) = \left( \frac{\sqrt{2} \cdot P_o}{\eta \cdot V_{in}} \cdot \operatorname{sen} \omega t \right) \cdot \left( \frac{1}{2} - \frac{1}{2} \cdot m_a \cdot \operatorname{sen} \omega t \right) \quad \text{Eq. 2-16}$$

Através da Eq. 2-16 chega se na Eq.2-17.

$$I_{Tmi}(\omega t) = \frac{1}{2} \cdot \frac{\sqrt{2} \cdot P_o}{\eta \cdot V_{in}} (\sin \omega t - ma \cdot \sin^2 \omega t) \quad \text{Eq. 2-17}$$

A corrente média e a corrente eficaz nos interruptores são obtidas integrando a Eq. 1-12 sobre um período do sinal de referência, lembrando que cada par de interruptores e diodos só conduz durante um ciclo.

Calculando a corrente média nos interruptores é possível encontrar a Eq.2-18:

$$I_{Tmed} = \frac{1}{2\pi} \int_0^\pi I_{Tmi}(\omega t) \cdot dt \quad \text{Eq. 2-18}$$

$$I_{Tmed} = \frac{1}{2\pi} \int_0^\pi \frac{1}{2} \cdot \frac{\sqrt{2} \cdot P_o}{\eta \cdot V_{in}} (\sin \omega t - ma \cdot \sin^2 \omega t) \cdot d\omega t \quad \text{Eq.2-19}$$

$$I_{Tmed} = \frac{\sqrt{2} \cdot P_o}{8\pi \cdot \eta \cdot V_{in}} (4 - ma\pi) \quad \text{Eq.2-20}$$

Calculando agora a corrente através da Eq.2-21:

$$I_{Tefi} = \sqrt{\frac{1}{T_S} \int_0^{D T_S} I_{in}^2 \cdot dt} \quad \text{Eq.2-21}$$

que resulta em:

$$I_{Tefi} = I_{in} \cdot \sqrt{D} \quad \text{Eq.2-22}$$

Substituindo  $I_{in}(\omega t)$  e  $D(\omega t)$  e efetuando as manipulações necessárias temos a Eq.2-23:

$$I_{Tefi}(\omega t) = \frac{\sqrt{2} \cdot P_o}{\eta \cdot V_{in}} \cdot \sin \omega t \cdot \sqrt{\frac{1}{2} \cdot (1 - ma \cdot \sin \omega t)} \quad \text{Eq.2-23}$$

$$I_{Tef} = \sqrt{\frac{1}{2\pi} \int_0^{\pi} (I_{Tefi})^2 \cdot dt} \quad \text{Eq.2-24}$$

$$I_{Tef} = \frac{P_o}{\eta \cdot V_{in}} \sqrt{\frac{1}{2\pi} \cdot \left( \frac{\pi}{2} - ma \frac{4}{3} \right)} \quad \text{Eq.2-25}$$

### 2.3.2 Equações para Esforços do Diodo

De maneira análoga ao procedimento adotado para os interruptores, a corrente através dos diodos em antiparalelo é determinada como sendo:

$$I_{Dmi} = \frac{1}{T_S} \int_{DT_S}^{T_S} I_{in} \cdot dt \quad \text{Eq.2-25}$$

Através da Eq. 2-25 chega se na Eq.2-26.

$$I_{Dmi} = I_{in} \cdot (1 - D) \quad \text{Eq. 2-26}$$

$$I_{Dmi}(\omega t) = \frac{1}{2} \cdot \frac{\sqrt{2} \cdot P_o}{\eta \cdot V_{in}} \cdot \left( \sin \omega t + ma \cdot \sin^2 \omega t \right) \quad \text{Eq.2-27}$$

A corrente eficaz para os diodos em antiparalelo pode ser calculada por:

$$I_{Dmed} = \frac{1}{2\pi} \int_0^{\pi} I_{Dmi}(\omega t) \cdot dt \quad \text{Eq.2-28}$$

$$I_{Dmed} = \frac{1}{2\pi} \cdot \int_0^{\pi} \frac{\sqrt{2} \cdot P_o}{2 \cdot \eta \cdot V_{in}} \left( \sin \omega t + ma \cdot \sin^2 \omega t \right) d\omega t \quad \text{Eq.2-29}$$

Através da Eq. 2-29 chega se na Eq.2-30.

$$I_{Dmed} = \frac{\sqrt{2} \cdot P_o}{8\pi \cdot \eta \cdot V_{in}} \cdot (4 + ma\pi) \quad \text{Eq.2-30}$$

A corrente eficaz para os diodos em antiparalelo pode ser calculada através a Eq.2-31

$$I_{Defi} = \sqrt{\frac{1}{Ts} \int_{DTs}^{Ts} I_{in}^2 \cdot dt} \quad \text{Eq. 2-31}$$

Trabalhando-se na Eq. 2-31 chega se na Eq.2-32.

$$I_{Defi} = I_{in} \cdot \sqrt{(1 - D)} \quad \text{Eq.2-32}$$

Para calculara a Corrente Eficaz através usa-se a Eq.2-33

$$I_{Def} = \sqrt{\frac{1}{2\pi} \int_0^{\pi} (I_{Defi})^2 \cdot dt} \quad \text{Eq.2-33}$$

$$I_{Def} = \sqrt{\frac{1}{2\pi} \int_0^{\pi} \left( \frac{\sqrt{2} \cdot P_o}{\eta \cdot V_{in}} \cdot \sin \omega t \right)^2 \cdot \left( 1 - \frac{1}{2} \cdot (1 - ma \cdot \sin \omega t) \right) \cdot dt} \quad \text{Eq.2-34}$$

Por fim tem-se:

$$I_{Def} = \frac{\sqrt{2} \cdot P_o}{\eta \cdot V_{in}} \sqrt{\frac{1}{2\pi} \cdot \left( \frac{\pi}{4} + ma \frac{2}{3} \right)} \quad \text{Eq.2-35}$$

A tensão de pico a qual estarão sujeitos os interruptores e a tensão reversa aplicada aos diodos terão o seu valor igual a da tensão da saída  $V_o$ , ou seja:

$$V_{Tpico} = +V_o \quad \text{Eq.2-36}$$

$$V_{Dpico} = -V_o \quad \text{Eq.2-37}$$

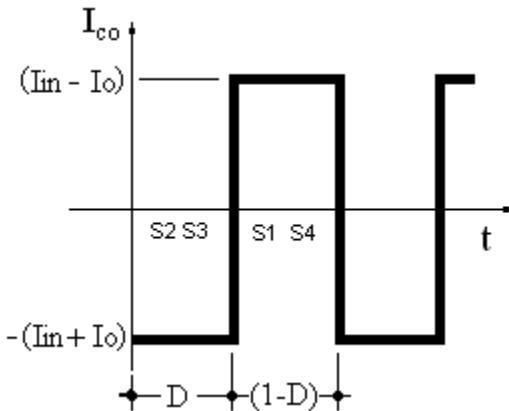

### 2.3.3 Equações para Cálculo do Capacitor

Analizando a corrente no capacitor no 1º quadrante de operação do conversor temos que esta corrente depende da corrente de entrada e da corrente de saída, como mostra a figura 2-4.

Figura 2-4 Etapas do funcionamento para um período de chaveamento no 1º quadrante.

Desta forma, admitindo que a corrente que saí no capacitor é uma corrente positiva, é possível traçar a forma de onda da corrente sobre o capacitor para um período de chaveamento, como mostra a figura 2-5.

Figura 2-5 Período de chaveamento para o 1º quadrante.

Através da figura 2-5 é possível calcular a corrente média no capacitor para um período de chaveamento através da Eq.2-38.

$$I_{Cmi} = \frac{1}{T_S} \left[ \int_0^{DT_S} -(I_{in} + I_o) dt + \int_{DT_S}^{T_S} (I_{in} - I_o) dt \right] \quad \text{Eq. 2-38}$$

Assim chega-se à Eq.2-39

$$I_{Cmi} = -I_{in}D - I_oD + I_{in} - I_o - I_{in}D + I_oD \quad \text{Eq. 2-39}$$

Logo, temos que a corrente média no capacitor depende da corrente da entrada, da corrente que vai para carga e da razão cíclica, como mostrado pela Eq.2-40.

$$I_{Cmi} = I_{in}(1 - 2D) - I_o \quad \text{Eq. 2-40}$$

O próximo passo é obter a corrente para um ciclo de rede. No entanto, nota-se que para um semiciclo a corrente média no capacitor tem sua equação modificada devido à mudança na polaridade da tensão da rede.

Para o 1º quadrante a corrente no capacitor é dada através da substituição das equações Eq. 2-7 e Eq. 2-10 na Eq. 2-20, como mostra a Eq.2-41.