# EMULATION OF NONLINEAR LOADS WITH ENERGY REGENERATION

Rafael Luís Klein, Angelo Fillipi de Paiva and Marcello Mezaroba

Núcleo de Processamento de Energia Elétrica – nPEE – Departamento de Engenharia Elétrica

Universidade do Estado de Santa Catarina UDESC – CCT

Campus Universitário Prof. Avelino Marcante s/n – Joinville/SC – Brasil

CEP 89223-100 – Phone Number +55 47 4009-7844

rafaelluisklein@gmail.com, fillipi.angelo@gmail.com, mezaroba@joinville.udesc.br

Abstract – This paper presents an nonlinear load emulator for testing AC power supplies and power equipment with energy regeneration capability. The structure is based on back to back three-phase PWM voltage source inverter (VSI). To achieve power balance, an independent control strategy for both PWM VSI is proposed. Experimental results are presented to verify the emulator performance draining a linear and nonlinear current from an autotransformer and regenerating the energy to the utility grid.

Keywords - Electronic load, energy regeneration, nonlinear load emulator.

### I. INTRODUCTION

The burn-in test is an indispensable step during the manufacture process of equipments such as uninterruptible power supplies (UPS), reactive static compensator, active power filters, AC power sources, electric generators and transformers.

The traditional method used to perform these burn-in tests consists in the association of resistors, capacitors, inductors and static converters, trying to reproduce the desired load profile defined by the end-user or standards for the given applications. Many times, this solution results in heavy and large equipments, besides the large energy consumption during the tests. Furthermore, every time a different load configuration is required, the reconfiguration of the load bank will be required, increasing the test time and resulting in high operating costs. Thus, not only the energy tested is wasted, but also the operation is inconvenient.

An alternative to reduce these problems is the use of electronic loads. The use of electronic loads brings the following advantages [1]:

- Reduced expenses due to energy savings (>80%)

- Lower air conditioning requirements

- Space savings

- Lower peak power demands

The commercial electronic loads are typically designed to dissipate the absorbed energy from the equipment under test (EUT). For applications above 10 kilowatts, the losses are unacceptable due the difficulty to dissipate the generated heat. Furthermore, the physical size of dissipative electronic loads makes the product unattractive.

To solve this problem, the electronic load should be able to return to the utility grid the electrical energy absorbed from the EUT.

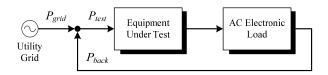

The Fig. 1 shows an application of a regenerative AC electronic load emulator.

Fig. 1. Block Diagram of an equipment coupled to a regenerative electronic load emulator.

The AC electronic load is connected between the output of the EUT and the utility grid. It absorbs current from EUT emulating the desired load profile and regenerates to the utility grid the energy absorbed during the test. Thus, it reduces the energy required to test the EUT.

Many papers have been published last years about AC electronic load emulators [1]-[19], applied to UPS [1]-[4], battery chargers or CC power supplies [4]-[6] and electronic ballast [7]. However, all the AC emulators referenced at the papers above are designed to absorb only sinusoidal current from the EUT, shifting the phase between current and voltage to control the reactive power flow.

This paper proposes the analysis of a nonlinear load emulator with energy regeneration capability based on a three-phase back-to-back converter structure. Initially it will be presented applications and standards for electronic equipments testing, the proposed circuit, followed by the control methodology and finally the experimental results obtained with a 4.5kVA prototype.

# II. APLICATION AND STANDARDS

The equipments which can be submitted to tests with electronic loads are mostly composed by devices that generate or process electrical energy. Among these devices, it is important to highlight:

- Uninterruptible power supplies (UPS)

- AC power supplies.

- Transformers.

- Active Filters.

- Electrical generators.

There are standards which standardize the load profile required for burn-in tests in electronic equipments.

The international standard IEC 62040-1 [20] applies to UPS and defines the load types to test an UPS. According to it, these equipments must be tested with linear and nonlinear loads. The load types quoted at the standard are:

- Resistor.

- Series resistor-inductor .

- Parallel resistor-inductor.

- Series resistor-capacitor.

- Parallel resistor-capacitor.

- Non-controlled rectifier with capacitive filter.

The standard IEEE C57.12.00-2000 [21] proposes limits to the harmonic currents in transformers. The maximum limit established is 5% of total harmonic distortion (THD) at the nominal fundamental current.

The standard IEEE 519-1992 [22] defines limits to the current distortion at a point of a electrical system according to its short-circuit current and voltage level.

Based on the quoted standards it is possible to generate reference signals to the electronic emulator according to the load profiles required to the burn-in test.

### III. PROPOSED EMULATOR

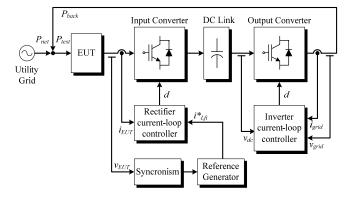

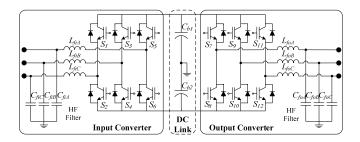

The basic configuration of the electronic load emulator with energy regeneration is shown at Fig. 2. The structure is composed by two converters, both current controlled. The chosen topology for their implementation is constituted by two three-phase four wire inverters interconnected by center-tapped DC link capacitor bank, as shown at Fig. 3.

This topology, besides the harmonic compensation, also allows compensation of the unbalanced load current. It means that the emulator can operate with any type of load.

The proposed control scheme has one converter which controls the power flow of the EUT, and the other that controls the regeneration of the power to utility grid.

The input converter is connected to the EUT to drain the current according the desired load profile. The references are generated by a digital signal processor (DSP) TMS320LF2812 [23] and are synchronized with the imposed voltage by the EUT.

The output converter is connected to the utility grid and sends the drained energy back to the utility grid with unity power factor. It also regulates the DC link voltage.

The main specifications of emulator are shown in table 1.

# IV. CONTROL DESIGN

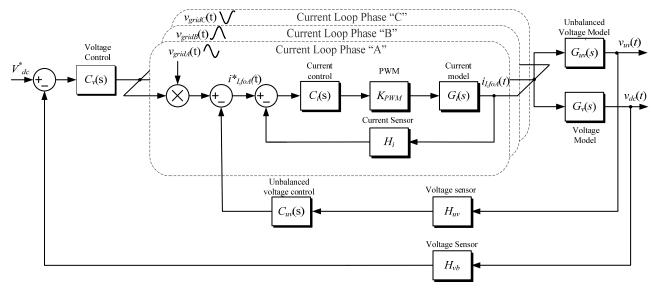

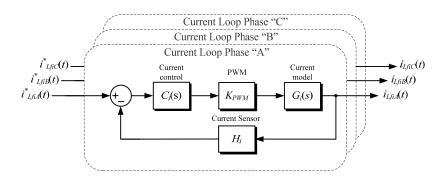

Fig. 4 and Fig. 5 show the block diagram of input and output converter control.

Fig. 2. Unifilar block diagram of regenerative AC electronic load emulator.

Fig. 3. Block diagram of power circuit.

TABLE I

Input and output converter specifications

| $P_{3\varphi} = 4.5 \text{ kVA}$                   | Total power                   |

|----------------------------------------------------|-------------------------------|

| $v_{DC} = 600 \text{ V}$                           | DC bus voltage                |

| $v_{grid} = 127 \text{ V}$                         | Phase to neutral Grid voltage |

| $v_{EUT}$ = 127 V                                  | Phase to neutral EUT voltage  |

| $B_i = 3 \text{ kHz}$                              | Input converter bandwidth     |

| $B_o = 1 \text{ kHz}$                              | Output converter bandwidth    |

| $i_{iA} - i_{iC} = i_{oA} - i_{oC} = 16 \text{ A}$ | Input and output peak current |

| $f_s = 50 \text{ kHz}$                             | Switching frequency           |

The output converter controller consist of three identical current feedback loops, one for each phase, in order to control the output current, one voltage feedback loop to control the DC link voltage and another one unbalanced-voltage feedback loop to keep the voltage on the DC link capacitor bank balanced.

The voltage control loop has a low response and determines the reference signal amplitude of current controller. The unbalanced-voltage control loop, is a DC level loop, acts on the average reference value of the current controller, in order to keep the DC link voltage balanced. The current control consists of three identical current loops, except for the 120 degrees phase shift from each other. The current loops have a fast response, allowing the decoupling of this with the voltage loop.

The input converter controller is composed by three identical current feedback loops, one for each phase, acting on the error signal generated by comparing the EUT current signal and a reference generated by a DSP synchronized with the imposed voltage by the EUT.

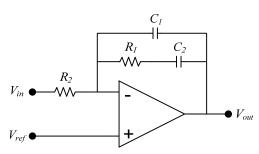

The current, voltage and unbalance-voltage control is designed with PI + pole compensator. This compensator provides phase lead at high frequencies, which enhances the responsiveness and stability of the system and phase lag at low frequencies which reduces the steady state error.

The cut-off frequency of the voltage and unbalanced voltage control are 6Hz and 0.6Hz respectively, these controllers should have a low response. Otherwise the current control is a fast control and its cut-off frequency is 8 kHz. All controls have phase margin between 30° e 90°.

Since the design specifications of the input and output converter are similar, the current controller design of the input converter is identical to the output converter.

The current loop transfer function is presented in equation (1)

$$G_i(s) = \frac{V_b}{L \cdot s} \cdot \frac{H_i}{Vm} \tag{1}$$

Fig. 4. Output converter control block diagram.

Fig. 5. Input converter control block diagram.

The voltage loop transfer function is presented in equation (2).

$$G_{v}(s) = \frac{3 \cdot m_{a}}{2 \cdot C_{b} \cdot s} \cdot \frac{K_{mp} \cdot K_{v} \cdot H_{vb}}{H_{i}}$$

(2)

The unbalanced voltage loop transfer function is presented in equation (3).

$$G_{uv}(s) = \frac{3}{2 \cdot C_b \cdot s} \cdot \frac{K_{uv} \cdot H_{vb}}{H_i}$$

(3)

Where:

C<sub>b</sub> - DC Link Capacitance

*H<sub>i</sub>* - Current Sensor Gain

$H_{vb}$  - Voltage Sensor Gain

$K_{mp}$  - Multiplier Gain

$K_{uv}$  - Unbalance-Voltage Control Attenuation

$K_v$  - Voltage Control Attenuation

L - Filter inductance

*m*<sub>a</sub> - Modulation Ratio

$V_b$  - DC link voltage

Vm - Pulse Width Modulator Gain

The proposed PI + pole compensator is shown in Fig. 6. Its transfer function is presented in equation (4).

Fig.6. PI + pole compensator.

$$C(s) = \frac{(1 + s \cdot R_1 \cdot C_2)}{s \cdot R_2 \cdot (C_1 + C_2) \cdot \left(1 + \frac{s \cdot R_1 \cdot C_1 \cdot C_2}{C_1 + C_2}\right)}$$

(4)

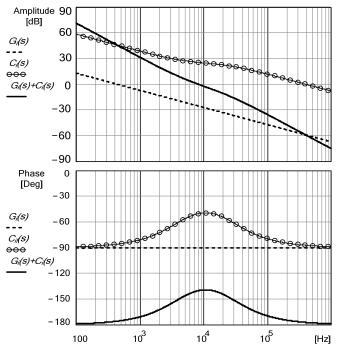

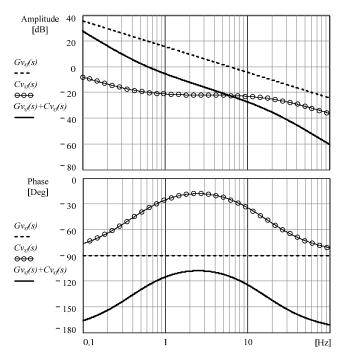

The current loop frequency response is shown in Fig. 7

Fig. 7. Current loop frequency response of the input and output converter

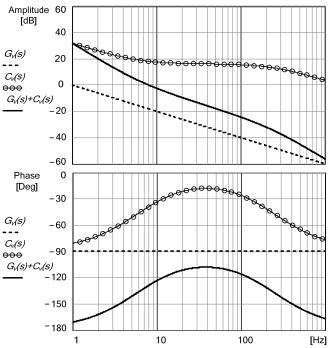

Fig. 8. Voltage loop frequency response of the output converter.

According to Fig. 7 the current loop with the designed controller presents phase margin equal to 40°, obeying the desired design value.

The voltage and unbalanced voltage loop with the designed controller presents phase margin equal to 43°, obeying the desired design value.

#### V. EXPERIMENTAL RESULTS

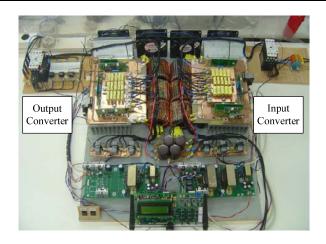

The proposed 4.5kVA load emulator has beer implemented and tested to verify the principle of operation.

Fig. 9. Voltage loop frequency response of the output converter.

The grid voltage and frequency is selected to 127V and 60Hz. The EUT used was a three-phase 4.5kVA autotransformer connected to the grid.

The prototype is shown in Fig. 10 and main prototype specifications are shown in Table 2.

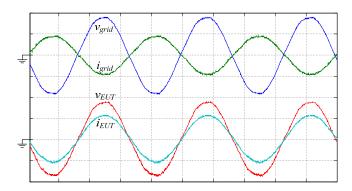

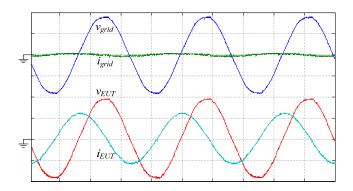

Fig. 11 shows the voltage and current from EUT for the resistive load emulation. The absorbed EUT current  $i_{EUT}$  is 5.5A peak, while the output converter current returned to the utility grid  $i_{grid}$  is 4.9A peak. The energy loss in the input and output converter is responsible for the difference between currents  $i_{EUT}$  and  $i_{grid}$ . The overall system efficiency can reach about 80% under full-load condition when emulating a pure resistance.

TABLE II Prototype Specifications

| $\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}_{\mathcal{L}}}}}}}}}}$ |                                        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| $S_I - S_{I2}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Switches: IRG4PF50WD                   |

| $D_1 - D_{12}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Switches Intrinsic Diodes              |

| $Cb_1 - Cb_2$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Electrolytic Capacitor: 8 x 470uF/450V |

| $Lfi_1 - Lfi_3$ , $Lfo_1 - Lfo_3$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Iron Powder Inductor: IT-560 Magmattec |

| $Cfi_1 - Cfi_3$ , $Cfo_1 - Cfo_3$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Polypropylene Capacitor: 5 x 1uF/630V  |

Fig. 10. Implemented prototype

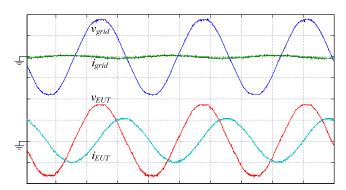

Fig. 12 shows the voltages and currents for the inductive load emulation with 90° phase angle. The EUT current is 5A peak, while the output converter current is practically the HF filter current.

Fig. 13 shows the voltages and currents for the capacitive load emulation with 90° phase angle. The EUT current is 5A peak, while the output converter current is practically the HF filter current.

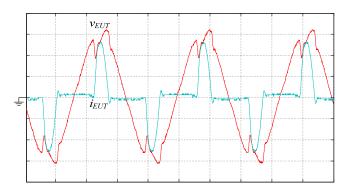

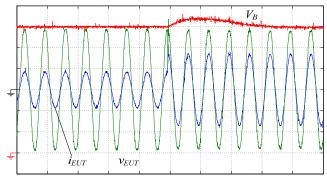

Fig. 14 shows the experimental results for nonlinear load emulation with a diode bridge rectifier. In this test the EUT current is 13A peak, with crest factor equal to 5. It can be observed the current distortion affects the EUT causing voltage notching.

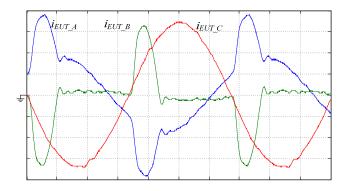

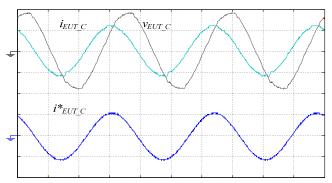

Fig. 15 shows the experimental results for three-phase currents with different load mode. The phase-A signal is composed by a resistive, inductive and diode bridge rectifier load. The phase-B signal is composed by diode bridge rectifier and phase-C is composed by capacitive load.

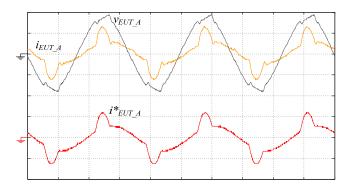

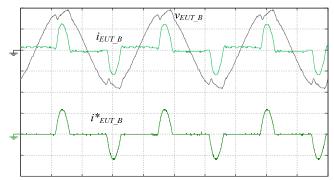

Fig. 16 to Fig.18 shows the voltage, current and reference current for the same signals sketched in Fig.15. It could be noted that the improved PI + pole controller has a good current tracking performance.

Fig. 17 and Fig. 18 shows a voltage sag in  $v_{EUT}$ , this is due the high crest factor of the emulated current. This test condition can be applicable to the harmonic test for power equipment such as power transformers.

Fig. 11. Resistive Load, grid and EUT voltage (100V/div), grid and EUT current (5A/div, 5ms/div)

Fig. 12. Inductive Load, grid and EUT voltage (100V/div), grid and EUT current (5A/div, 5ms/div)

Fig. 13. Capacitive Load, grid and EUT voltage (100V/div), grid and EUT current (5A/div, 5ms/div)

Fig. 14. Rectified load, EUT voltage (50V/div), EUT current (5A/div, 5ms/div)

Fig. 15. Three-phase nonlinear loads, current (5A/div, 5ms/div)

Fig. 16. Nonlinear load, EUT voltage (100V/div), EUT current (10A/div), EUT current reference (4V/div, 5ms/div)

Fig. 17. Rectified load, EUT voltage (100V/div), EUT current (10A/div), EUT current reference (4V/div, 5ms/div)

Fig. 18. Capacitive load, EUT voltage (100V/div), EUT current (10A/div), EUT current reference (4V/div, 5ms/div)

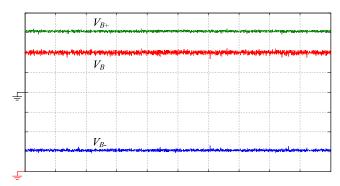

Fig. 19. DC bus voltage, (100V/div, 5ms/div)

Fig. 20. Load step 100-50%, ( $v_{EUT}$ :60V/div,  $V_B$ :100V/div 10A/div, 25ms/div)

Fig. 19 shows the DC link voltages whose voltages are controlled in 300V and -300 for each of the capacitor banks.

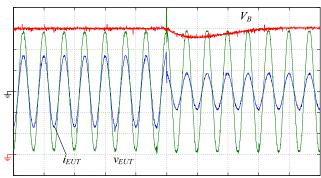

Fig. 20 and Fig. 21 shows the experimental results for a load step from 100% to 50% and 50% to 100% respectively emulating a resistive load.

Fig. 21. Load step 50-100%, ( $v_{EUT}$ :60V/div,  $V_B$ :100V/div 10A/div, 25ms/div)

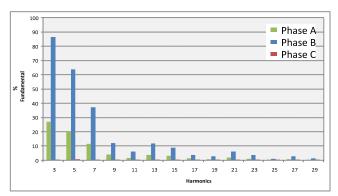

Fig. 22. Total harmonic distortion (THD) of three-phase nonlinear loads

We can observe the variation of DC bus voltage and voltage compensator response to regulate de DC link

Fig. 22 shows the harmonic analysis of three-phase current emulated in Fig. 15. The load current THDs are 36.5%, 115% and 1.4% respectively.

# VI. CONCLUSION

In this paper it was presented the applications, system architecture, operating principles, controller design and experimental results of the regenerative AC electronic load emulator.

The proposed controller attended all project goals and provided stable operation during all the practical tests with linear and nonlinear load emulation.

The load energy was regenerated to utility grid with unity power factor, saving a large amount of energy during the practical test.

According to the experimental results, the emulated load models behaved as a real passive and active load.

All the waveforms in the practical tests of the proposed emulator were applied to an autotransformer.

Finally, the main advantages were, reduced expenses due to energy savings, setup time reduced, lower air conditioning requirements, space savings and lower peak power demands.

### REFERENCES

[1] S. Gupta, V. Rangaswamy, R. Ruth, "Load bank elimination for UPS testing", in Proc. IEEE, pp. 1040–1043, 1990.

- [2] C. A. Ayres, I. Barbi, "A family of converters for UPS production burn-in energy recovery", in Proc.IEEE Transactions on Power Electronics, pp. 615–622, 1997.

- [3] C. L. Chu, J. F. Chen, "Self-load bank for UPS testing by circulating current method", IEE Proc.-Electr. Power Applications, pp. 191–196, 1994.

- [4] M. T. Tsai, "Comparative investigation of the energy recycler for power electronics burn-in test", IEE Proc.-Electr. Power Applications, pp. 192–198, 2000.

- [5] J. L. Dantas, "Reciclador de energia para testes de burnin em fontes cc para telecomunicações", Dissertação de mestrado, Universidade Federal de Ceará, 2006.

- [6] C. A. Ayres, I. Barbi, "Power recycler for DC power supplies burn-in test: Designand experimentation", In: APEC'96 – Applied Power Electronics Conference and Exposition, p. 72-78, 1996

- [7] C. Zimmermann Jr., "Regenerador de energia com elevado fator de potência para o teste de burn-in de reatores eletrônicos de 250W", Dissertação de mestrado, Universidade Federal de Santa Catarina, 2004.

- [8] M. Y. Change, J. Y. Lin, S. L. Jung, Y. Y. Tzou, "Design and implementation of a real-time lossless dynamic electronic load simulator", IEEE Proc, pp734-739, 1997.

- [9] R. Vázquez, E. Olías, A. Lázaro, A. Barrado and J. Pleite, "Implementation of a loss-free programmable AC load", IEEE Proc., pp. 630–635, 1998.

- [10]C. A. Ayres, "Recicladores de potência", Tese de Doutorado em Engenharia Elétrica, Universidade Federal de Santa Catarina, 1996.

- [11]F. Li, Y. P. Zou, C. Z. Wang, W. Chen, Y. C. Zhang, J. Zhang, "Research on AC Electronic Load Based on Back to Back Single-phase PWM Rectifiers", IEEE proc., 2008.

- [12]C. Wang, Y. Zou, K. Jia, F. Li, Y. Zhang, X. She, "Research onthe Power Electronic Load Based on Repetitive Controller", IEEE Proc., 2008.

- [13]Y. Srinivasa Rao; Mukul Chandorkar, "Electrical Load Emulation using Power Electronic Converters", TENCON, 2008.

- [14]Y. Zhou, Lei Wang, Xin Chen, "Research on Digital Controlled Converter for AC Power Electronics Burn-In Test with Energy Feedback", ICEMS, 2008.

- [15]X. She, Y. She, C. Z. Wang; Y. P. Zou, "AC Electronic Load and its application in power system simulation", IEEE Proc., 2008.

- [16]J. W. Baek, M. H. Ryoo, J. H. Kim; J. S. Lai, "50kVA Regenerative Active load for power test system", PEC 2007

- [17]J. Zhao, S. Pan, X. Wang, "High power energy feedback AC electronic load and its application in power system dynamic physical simulation", IEEE Proc., 2007.

- [18]M-T. Tsai; C. Tsai, "Energy Recycling for Electrical AC Power Source Burn-In Test", IEEE Proc., 2000.

- [19]M. T. Tsai; T. J. Cheng; C. Tsai, "High-Efficiency Energy Recycling System for AC Power Source Burn-In Test", PEDS 1999.

- [20]General and Safety Requirements for UPS, IEC 62040-1, 2008.

- [21]IEEE Standard General Requirements for Liquid-Immersed Distribution, Power and Regulation Transformer, IEEE Standard C57.12.00, 2000.

- [22] IEEE Recommended Practices and Requirements for Harmonic Control in Electrical power Systems, IEEE Standard 519, 1992.

- [23] Mezaroba, Marcello; Heerdt, Joselito Anastácio; Batschauer, Alessandro Luiz; Giacomini, Neomar. Gerador de sinais periódicos genéricos para utilização em fontes de alimentação CA. In: Congresso Brasileiro de Automática, 2006, Salvador, 2006.