# DESIGN OF A REVERSIBLE PFC WITH DIGITAL CONTROL USING DSP

Julio Cezar Raycik and Marcello Mezaroba Power Electronics Laboratory – LEPO State University of Santa Catarina – UDESC P.O. Box 631, Zip Code 89.223-100, Joinville, SC, Brasil raycik@joinville.senai.br, mezaroba@joinville.udesc.br

Abstract - This work shows a methodology to development of control using a digital processing by DSPs. For the application of this methodology was used a single-phase rectifier with reversibility in current. To this propose was take all the equation applied in this converter by qualitative analysis of variable of voltage and current that are evolved in the process. Is showed the main equations taken. It is also showed the technique of the controller design using this conventional techniques, because the target is to reduce the academic strong ness in the development of research work of new converters using concepts that were already used before and to simplify the knowledge of this process using DSPs, through a using high level programming language which is possible with the use of tools that simplify the code.

*Keywords* - DSP Controler, Current Rectifier, Full Brigdh, Rectifier, Digital Control.

#### I. INTRODUCTION

This converter is used frequently in power factor correction that need regeneration of energy that comes of motor brakes, in DC link voltage regulation. Also is used in other application like, active filters, and co-generation.

In this study will be used the method of Mean Value Control used in almost of works, but, the enface is the use of technique of digital control.

#### II. CONTROL BLOCK DIAGRAM USING DSP

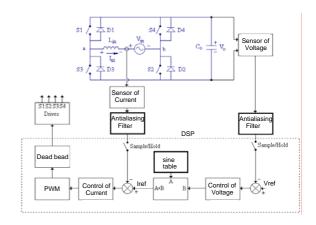

The converter structure studied is showed on figure 1 that is connected to line through an inductor Lin. The side CC is connected to capacitor of filtering Co.

To use a digital controller is necessary to do some addiction in the classic diagram of control, looking to some control characteristic, as showed as Figure 1.

The Anti-aliasing filters are introduced to reduce the components of frequency over the middle of sample frequency. This effect is caused when a signal of high frequency takes the form of a signal with a under frequency.

The circuits of sample and hold are intern circuits in DSP to realize the sample of dates by AD converter.

Fig. 1. Block Diagram of Converter Control.

#### III. CONVERTER TRANSFER FUNCTION

#### A. Transfer Function to Current Control

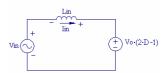

The Figure 2 shows the model to big signals to this converter, in function of switching frequency, where the voltage Vin represents the converter voltage input, Lin is the filtering inductor and the output is represented by CC source, where the middle value of this source, depends of voltage on the capacitor Vo and the cyclic ration D as showed on Figure 2

Fig. 2. Model to big signals.

The current transfer function Iin in function of D variation, i.e.  $\Delta D$ , is showed on (1).

$$\frac{\Delta I_{in}(s)}{\Delta D(s)} = \frac{2 \cdot V_o}{s \cdot L_{in}} \tag{1}$$

# B. Transfer Function to Voltage Control

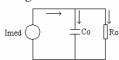

In Figure 3 is showed the circuit used to deduce the transfer function to Voltage Control.

Fig. 3. Simplified converter circuit to voltage control.

The current produced by the source of current is equal the addition of current of capacitor and resistor at the load, so:

$$(2D-1) \cdot I_{Lin} = C_o \cdot \frac{dV_o}{dt} + \frac{V_o}{R_o}$$

(2)

Using Laplace in (2), come the (3) that represent the transfer function voltage loop.

$$\frac{V_o(s)}{I_{Lin}(s)} = \frac{R_o \cdot (2D - 1)}{1 + s \cdot R_o \cdot C_o}$$

(3)

# IV. DESIGN METHODOLOGY TO DIGITAL CONTROLLERS

In Ogata [4], is showed some procedures to make a DESIGN when digital controller is used.

- 1. Take G(z) initially, i.e. the transformed  $\mathbf{z}$  of the plant after the sample. Then the bilinear transformed is used to take the transfer function to the  $\mathbf{w}$  dominium.

- 2. Substitute  $\mathbf{j}\boldsymbol{\omega}$  for  $\mathbf{j}\boldsymbol{\upsilon}$  in  $\mathbf{G}(\mathbf{j}\boldsymbol{\omega})$  and trace the Bode diagram to  $\mathbf{G}(\mathbf{j}\boldsymbol{\upsilon})$ .

- 3. Then, with the diagram, read the static error and gap of the phase and gain.

- 4. Using a unitary gain to the low frequency to the function of controller in discrete time, **H(w)**, determinate the gain of system that satisfies the constant of static error. Then, using the techniques of DESIGN conventional to the systems of control in continuous time, to determine the poles and zeros of transfer function of digital controller.

- Realize the transformed of the transfer function of controller H(w) to H(z) using the inverse bilinear transformation, obtaining the discrete transfer function of controller.

- 6. Implement the discrete function  $\mathbf{H}(\mathbf{z})$ , using the differences equation, through a computational algorithm.

## V. DIGITAL CONTROLLER DESIGN

The requirements to the DESIGN are gived by [1], [2] and [3]. The phase changes between  $45^{\circ}$  and  $90^{\circ}$ , the inclination of the curve of gain to the open system loop should be -20db/decade, null statistic error, the through frequency to gain curve in the open system loop should be four times smaller than the switching frequency, and the switching frequency should be 10 times smaller than the sample frequency.

# VI. CURRENT CONTROLLER DESIGN

one pole in origin, so the static error is null and it is stable, so the inclination at crossover frequency is -20dB/decade;

With (4) is possible to get some conclusions: It has only

$$G_i(w) = K_{PWM} \cdot K_{AD} \cdot K_i \cdot \frac{V_o}{L_{in}} \cdot \frac{1 - \frac{T_{o}}{2}w}{w}$$

(4)

Where:

Ta - Rate of Sampling  $K_{PWM}$  - Gain of PWM

$K_{AD}$  - Gain of Analog to Digital Converter

Ki -Gain of Corrent Sensor

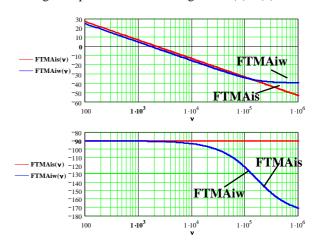

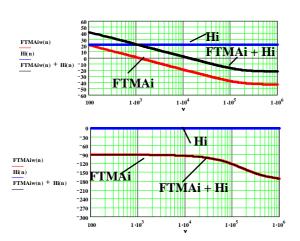

Figure 4 presents the bode diagram of (1) e (4).

Fig. 4. Frequency answer to continuous and discrete current plant.

# B. Current Controller Design

With a gain of FTMA<sub>i</sub> without the controler,  $H_i(w)$ , is – 3,63dB for a frequency of 12,5 kHz, the gain of controller,  $k_{\text{Hi}}$ , should be DESIGNed to present a gain of 3,63dB, than:

$$H_{i}(w) = 7,46$$

(5)

# C. Controller Influence Analyze

To show how the inclusion of the controller  $H_i(w)$  in FTMA<sub>i</sub> affects the answer of system, Bode Diagram of transfer function presented in figure on figure 4, together with the answer of the system without controller  $(G_i(w))$  and FTMA<sub>i</sub> function.

# D. Inverse Transformed of Controller

With the equation of controller in  $H_i(w)$ , is possible to reach  $H_i(z)$ :

$$H_{z}(z) = 7.46$$

(6)

#### E. Difference Equation for Current Controller

Transforming (6) in a difference equation, taking into account the shifting theorem:

$$u_i(n) = 7.46 \cdot e_i(n)$$

(7)

Fig. 5. Answer of FTMA<sub>i</sub> with current controller.

#### VI. DESIGN OF VOLTAGE CONTROLLER

#### A. Transfer Function to s Plane

The principles of management the design of the voltage loop controller are the same used by management of design of current controller, then one parallel can be traced and the DESIGN step can be generalized.

The transfer function to s plane was showed in (3)

## B. Transfer function to w Plane

The transformation of (3) to w plane result in (8).

$$G_{v}(w) = A_{1} \cdot \left( \frac{1 - e^{-Ta/A_{2}} + w \cdot \frac{Ta}{2} \left( e^{-Ta/A_{2}} - 1 \right)}{1 - e^{-Ta/A_{2}} + w \cdot \frac{Ta}{2} \left( 1 + e^{-Ta/A_{2}} \right)} \right)$$

(8)

#### Where:

Ta - Rate of Sampling

A1 - Constants in function of Vin, Vo and Ro

A2 - Constants in function of Ro and Co

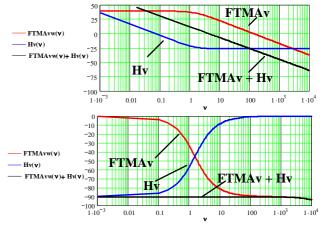

Figure 6 present the analyse of resposte in frequency of (3) e (8).

## C. Transfer Function to Open Loop (FTMAv)

$$FTMA_{v}(w) = H_{v}(w) \cdot G_{v}(w) \cdot k_{v}$$

(9)

## D. Design of Controller Voltage

$$H_{\nu}(w) = 0.0464 \cdot \frac{(w+9.42)}{w}$$

(10)

Fig. 6. Frequency answer to continuous and discrete voltage plant.

### E. Controller Influence Analyze

Fig. 7. Answer of FTMA<sub>i</sub> with controller of voltage.

## F. Inverse Transformer of Controller

$$H_{\nu}(z) = \frac{(0.0460008671 \cdot z - 0.0459991329)}{z - 1} \tag{11}$$

### G. Difference Equation for Current's Controller

Translate (11) in a difference equation, account the sampling theorem:

$$u_{n}(n) = 0.046 e_{n}(n) - 0.04599 e_{n}(n-1) + u_{n}(n-1)$$

(12)

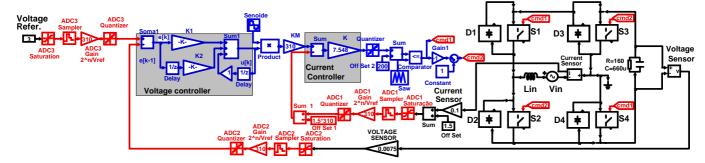

Fig. 8. Block Diagram

#### VI. NUMERIC SIMULATION

To the evaluation of control used at the DESIGN is necessary to make some simulation using computing methods to observe the system answers. The software used was the MATLAB, more specifically the SIMULINK, where were used the power system library and discrete blocks to simulate the ADC and calculation made by the DSP

The Block Diagram used to simulation is presented in Figure 8.

#### A. Simulation Results

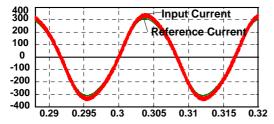

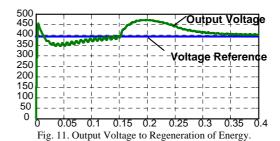

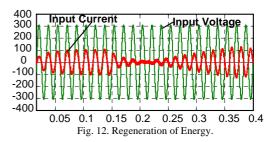

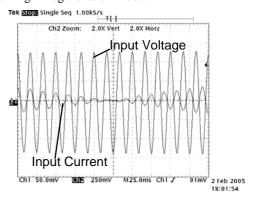

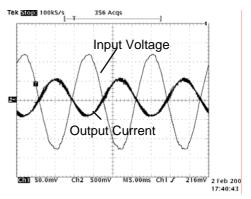

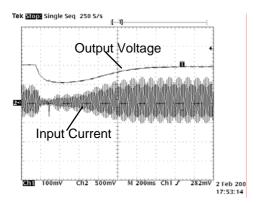

The results of simulation are showed here, where is possible observe the input and output current and voltage through the Figures 9, 10, 11 and 12.

Fig. 9. Reference and Input Current.

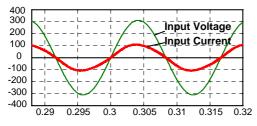

Fig. 10. Input Voltage e Current.

#### B. Regeneration Mode

## VII. PRACTICAL RESULTS

Following the equations of the mathematical analysis, the information had been concentrated thorough tables.

Thus, the initial design specifications, and the main results can be observed in the Tables 01 and 02, respectively.

TABLE I Initial Design Specifications

| Variable Description  | Values              |

|-----------------------|---------------------|

| Sample Frequency      | fa=500kHz           |

| Switching Frequency   | fs=-50kHz           |

| Output Voltage        | $V_o$ =400 $V$      |

| Maximum Input Voltage | $V_{inpico} = 311V$ |

| Current Gain          | Ki=0,0078           |

| Voltage Gain          | Kv=0,00638          |

| Output Capacitor      | $C_o = 663.5 \mu F$ |

| Output Resistance     | $R_o = 160$         |

| Output Power   | $P_o = 1kW$    |

|----------------|----------------|

| Input Inductor | $L_{in} = 6mH$ |

TABLE II

Main Components Specifications

| Variable Description | Values                                                                  |

|----------------------|-------------------------------------------------------------------------|

| S1, S2, S3 and S4    | IRGP35B60PD                                                             |

| D1, D2, D3 and D4    | Switches intrinsic diodes                                               |

| Lin                  | Ferrite Inductor: EE65/39, nfp=19, wires=27AWG, 93 turns, and lg=1,4mm. |

| Cout                 | Electrolytic Capacitor 3x220μF                                          |

#### A. Change load

Figure 13 is presented the waveform take with reduction of load.

Fig. 13. Change of load (step of 100%).

## B. Input Voltage Variation

Figure 14 and 15 is showed the test of variation of the input voltage.

Fig. 14. Reduction of Input Voltage (20%).

Fig. 15. Step of Input Voltage (step of 20%).

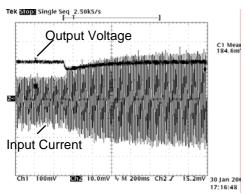

# C. Regeneration Mode

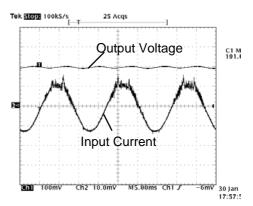

The *Figure 16*, *17*, *18* and *19* shows the converter working in regeneration mode.

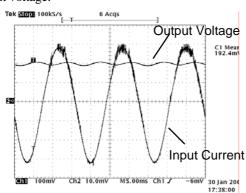

Fig. 16. Working in Energy Regeneration Mode.

Fig. 17. Working in Inverter Mode.

## VIII. CONCLUSION

This paper showed a Design of a Reversible PFC with Digital Control Using DSP, this study will be used to implementation of three-phase converter in a future work. Also presented the implementation, and some dates that were taken.

Fig. 18. Though to Regeneration Mode (Inverter).

Fig. 19. Come back to Rectifier Mode.

The converter was not tested in the nominal rated power because a limitation of our laboratory equipment. But was possible to observe the efficiency of controller through of the simulation process. Also was observed the simplification of design controller where were used the conventional techniques what can help in the reutilization of DESIGN already existent, doing that the fact of using use a digital controller not do add more effort to the DESIGN and the study of structure of converter became the main target of research. Lastly it was taken some practical results of implementation where the main result

was the functioning in regeneration mode, as obtained in the simulation.

#### IX. REFERENCES

- [1] TOMASELLI, Luis Cândido; <u>Controle de um préregulador com alto fator de potência utilizando o controlador DSP TMS320F243</u> Dissertação de Mestrado, UFSC, Florianópolis, SC, 2001.

- [2] BATSCHAUER, Alessandro Luiz; CHELAB NETO, Anis Cezar; PETRY, Clóvis Antônio; Conversor Boost operando em condução contínua aplicado à correção de fator de potência empregando controle da corrente de entrada por valores médios instantâneos; Estudo para Mestrado, UFSC, Florianópolis, SC, 2001.

- [3] BARBI, Ivo; <u>Projeto de Fontes Chaveadas</u>. Edição do Autor. Florianópolis, 2001.

- [4] OGATA, Katsuhiko <u>Modern Control</u> <u>Engineering</u>. Third Edition. Prentice Hall, New Jersey, 1997.

- [5] <u>TMS320F/C24x DSP Controllers CPU and Instruction Set Literature Number SPRU 160C</u>, Texas Instruments. Jun/1999.

- [6] TMS320LF/LC240xA DSP Controllers System and Peripherals Literature Number SPRU357, Texas Instruments. Rev. Dez/2001.

- [7] OGATA, Katsuhiko; <u>Discret-Time Control Systems</u>. Second Edition. Prentice Hall, New Jersey, 1994.

- [8] RAYCIK, Julio César; <u>Simulação de um</u> <u>Retificador de Corrente Monofásico</u>; Relatório desenvolvido para a Disciplina de Acionamento Elétricos Mestrado em Automação Industrial. UDESC Joinvile, SC. OUT, 2002.

- [9] CARDOSO, Fabiano Luz; RAYCIK, Júlio César; <u>Filtro Ativo Monofásico</u>; Relatório desenvolvido para a Disciplina de Correção de Fator de Potência Mestrado em Automação Industrial. UDESC Joinvile, SC. JUN, 2003

- [10] BARCZAK, Czeslau L; <u>Controle Digital de Sistemas Dinâmicos, Projeto e Análise</u>; Editora Edgard Blücher Ltda, São Paulo, SP. 1994.